Abstract

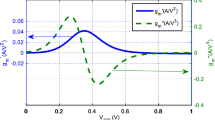

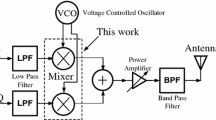

In the present paper, a linearization technique is proposed for double-balanced active inductor-less mixer based on the interaction of two nonlinear approaches. The proposed procedure utilizes multiple-gate and second harmonic injection techniques in order to simultaneously enhance the third-order intercept point (IIP3) and second-order intercept point (IIP2). The full Volterra series analysis of transconductance stage of the proposed mixer is presented to demonstrate the effective technique in detail. Simulations are performed utilizing a TSMC \(0.18\, \upmu \hbox {m}\) CMOS technology. Compared with the conventional Gilbert cell mixer, the simulations suggest improvements of 18.6 dBm and 54 dBm in IIP3 and IIP2 of the proposed mixer, respectively. The mixer has a conversion gain of 20.3 dB while 3.21 mA is drawn from a 1.8 V power supply.

Similar content being viewed by others

References

M. Asghari, M. Yavari, Using interaction between two nonlinear systems to improve IIP3 in active mixers. Electron. Lett. 50(2), 76–77 (2014)

M. Asghari, M. Yavari, Using the gate–bulk interaction and a fundamental current injection to attenuate IM3 and IM2 currents in RF transconductors. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 24(1), 223–232 (2016)

F. Belmas, F. Hameau, J.-M. Fournier, A low power inductorless LNA with double Gm enhancement in 130 nm CMOS. IEEE J. Solid- State Circuits 47(5), 1094–1103 (2012)

J. Cárdenas, J. Galaviz-Aguilar, J. Perez, A. Tellez, Modeling memory effects in RF power amplifiers applied to a digital pre-distortion algorithm and emulated on a DSP-FPGA board. Integr. VLSI J. 49(1), 49–64 (2015)

P.G. Drennan, C.C. McAndrew, Understanding MOSFET mismatch for analog design. IEEE J. Solid-State Circuits 38(3), 450–456 (2003)

K. Dufrene, Z. Boos, R. Weigel, Digital adaptive IIP2 calibration scheme for CMOS downconversion mixers. IEEE J. Solid-State Circuits 43(11), 2434–2445 (2008)

I. Elahi, K. Muhammad, P.T. Balsara, IIP2 and DC offsets in the presence of leakage at LO frequency. IEEE Trans. Circuits Syst. II Exp. Briefs 53(8), 647–651 (2006)

M. El-Nozahi, A.A. Helmy, E. Sanchez-Sinencio, K. Entesari, An inductor-less noise-cancelling broadband low noise amplifier with composite transistor pair in 90 nm CMOS technology. IEEE J. Solid- State Circuits 46(5), 1111–1122 (2011)

R. Harjani, L. Cai, Inductorless design of wireless CMOS frontends, in IEEE ASICON (2007), pp. 1367–1370

T.H. Jin, T.W. Kim, A 6.75 mW +12.45 dBm IIP3 1.76 dB NF 0.9 GHz CMOS LNA employing multiple gated transistors with bulk bias control. IEEE Microw. Wirel. Compon. Lett 21(11), 616–618 (2011)

S. Lou, H.C. Luong, A linearization technique for RF receiver front-end using second-order-intermodulation injection. IEEE J. Solid-State Circuit 43(11), 2404–2412 (2008)

L. Ma, Z. Wang, J. Xu, A1-V current-reused wideband current-mirror mixer in 180-nm CMOS with high IIP2. Circuits Syst. Signal Process. 36(5), 1806–1817 (2017)

D. Manstretta, M. Brandolini, F. Svelto, Second-order inter-modulation mechanisms in CMOS downconverters. IEEE J. Solid-State Circuits 38(3), 394–406 (2003)

M. Mollaalipour, H. Miar-Naimi, An improved high linearity active CMOS mixer: design and Volterra series analysis. IEEE Trans. Circuits Syst. I Regul. Pap. 60(8), 2092–2103 (2013)

B. Razavi, RF Microelectronics (Prentice-Hall PTR, Upper Saddle River, NJ, 1998)

D.D. Silveira, P.L. Gilabert, A.B. Santos, M. Gadringer, Analysis of variations of volterra series models for RF power amplifiers. IEEE MWCL 23(1), 442–44 (2013)

M.B. Vahidfar, O. Shoaei, A high IIP2 mixer enhanced by a new calibration technique for zero-If receivers. IEEE Trans. Circuits Syst. II Exp. Briefs 55(3), 219–223 (2008)

P. Wambacq, W.M. Sansen, Distortion Analysis of Analog Integrated Circuits (Kluwer, Norwell, MA, 1998)

Q. Wan, D. Xu, H. Zho, J. Dong, A complementary current-mirror-based bulk-driven down-conversion mixer for wideband applications. Circuits Syst. Signal Process. 37(9), 3671–3684 (2018)

T. Wook Kim, B. Kim, K. Lee, Highly linear receiver front-end adopting MOSFET transconductance linearization by multiple gated. IEEE J. Solid-State Circuits 39(1), 223–229 (2004)

X.Y.Z. Xiong, L.J. Jiang, J.E. Schutt-Aine, W.C. Chew, Volterra series-based time-domain macromodeling of nonlinear circuits. IEEE Trans. Compon. Packag. Manuf. Technol. 7(1), 39–49 (2017)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendices

Appendices

1.1 A: Expanded Equation in Multiple-Gate Transistors

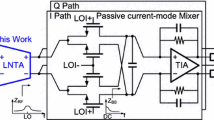

The drain current of M1 and M2 in Fig. 2 can be expressed as:

where \(\mu _{0}\) denotes the zero-field mobility and \(V_{\mathrm{sat}}\) and \(\theta \) are the saturation velocity of carrier and the effect of the vertical field, respectively. If the second term in the denominator remains much less than unity, it is possible to rewrite Eqs. (29) and (30) as, respectively, Eqs. (31) and (32) using the approximation: \((1+\varepsilon )^{-1} \approx 1 - \varepsilon + \varepsilon ^2\) [1]

For simplicity, Eqs. (31) and (32) can be rewritten as Eqs. (33) and (34), respectively:

where \(k_{1}=\frac{1}{2}\mu _{0}C_{\mathrm{ox}}\frac{W_{1}}{L_{1}}\), \(k_{2}=\frac{1}{2}\mu _{0}C_{\mathrm{ox}}\frac{W_{2}}{L_{2}}\), \( a_{1}=(\frac{\mu _{0}}{2V_{\mathrm{sat}}L_{1}} + \theta )\) and \(a_{2}= (\frac{\mu _{0}}{2V_{\mathrm{sat}}L_{2}} + \theta )\). Now, by applying KCL at the drains of transistors, one obtains:

By summing \( I_{\mathrm{D}1}\) and \(I_{\mathrm{D}2}\), and classification of \(I_{\mathrm{D}}\), the coefficients A1, A2, and A3 can be given as follows as well as what is shown in Eqs. (5)–(7) in Sect. 3.

1.2 B: Expanded Volterra Series Analysis of Transconductance Stage

The drain current of \(M_{1b}\) and \(M_{2b}\) in Fig. 3 can be expressed as:

Now, by assuming \(g_{\mathrm{m}_{1b}} = g_{\mathrm{m}_{2b}}\), \(g_{\mathrm{m}_{1b}}^{'} = g_{\mathrm{m}_{2b}}^{'}\), and \(g_{\mathrm{m}_{1b}}^{''} = g_{\mathrm{m}_{2b}}^{''}\), and applying KCL at the drain node of transistors, \( I_{\mathrm{Dt}}\) (as shown in Fig. 3) can be obtained as:

Now, by injecting \(I_{\mathrm{Dt}}\) current into the RLC network, \(V_{\mathrm{D}}\) is obtained as:

where \(Z_{\mathrm{D}} = R_{\mathrm{D}} \parallel j\omega L_{\mathrm{D}} \parallel \frac{1}{j\omega C_{\mathrm{D}}}\), thus:

The voltage at the output node of subsystem B is related to the input voltage signal. Accordingly, it can be expressed based on Volterra series as follows:

where \(B_{1}\), \(B_{2}\), and \(B_{3}\) are Volterra kernels of \(V_{\mathrm{out}}\). The goal is to obtain \(B_{1}\), \(B_{2}\), and \(B_{3}\). Hence by applying KCL at the output node (\(I_{3} = I_{1} - I_{2}\)), these currents can be obtained as:

where \(Z_{\mathrm{L}} = R_{\mathrm{out}} \parallel \frac{1}{j\omega C_{\mathrm{P}}}\) and \(R_{\mathrm{out}} = r_{\mathrm{o}_{3b}} \parallel r_{\mathrm{o}_{5b}}\). Substituting of (43)–(45) in \(I_{3} = I_{1} - I_{2}\) and grouping the variables, the coefficients of \(v_{\mathrm{in}}\), \(v_{\mathrm{in}}^{2}\), and \(v_{\mathrm{in}}^{3}\), i.e., \(B_{1}\), \(B_{2}\), and \(B_{3}\), can be expressed according to Eqs. (15)–(17).

The output current of subsystem A is related to the input voltage signal. Thus, it can be expressed based on Volterra series as follows:

where \(H_{1}\), \(H_{2}\), and \(H_{3}\) are Volterra kernels of output current. \(I_{\mathrm{out}}\) can be obtained as:

Now, by substituting Eq. (42) in (47) as well as using Eqs. (15)–(17), and (5)–(7) instead of \(A_{1}\), \(A_{2}\), and \(A_{3}\), Eq. (47) can be rewritten as:

Now, all Volterra kernels obtained in Eqs. (5)–(7) and (15)–(17) should be substituted into Eq. (48) in order to achieve Volterra kernels of the output current, as given in Eqs. (19)–(21).

\(M_{1c}-M_{4c}\) are added to the circuit to enhance IIP2.These transistors affect \(H_{2}\) (second coefficient of Volterra kernels of \(I_{\mathrm{out}}\)). Figure 4 shows these added transistors. \(I_{\mathrm{out}}^{'}\) can be expressed as:

where \(C_{p2}\) is the total parasitic capacitance of the drain and gate of \( M_{1c}\) and \( M_{3c}\). Thus, \(I_{\mathrm{out}}^{'}\) can be expressed as:

By applying KCL at the output node of subsystem B, the total current of transconductance stage is obtained by summing \(I_{\mathrm{out}}\) and \(I_{\mathrm{out}}^{'}\) as in:

Substituting Eqs. (48) and (50) in equation (51), Volterra kernels of total current can be obtained. As seen, \(H_{1}\) and \(H_{3}\) do not change but \(H_{2}\) changes as shown in Eq. (25).

Rights and permissions

About this article

Cite this article

Ataei Siah Bidi, A., Karimi, G. Design of High Linearity Inductor-Less Active CMOS Mixer Based on Volterra Series Analysis. Circuits Syst Signal Process 39, 4810–4828 (2020). https://doi.org/10.1007/s00034-020-01407-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-020-01407-9