Abstract

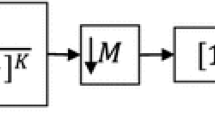

The cascaded integrator–comb (CIC) filter is a key building block for communication and sample rate conversion systems that require efficient implementation. One such example is in satellite applications. Space applications have the problem of being highly susceptible to cosmic radiation, which in turn has the possibility of corrupting data. It is therefore necessary to devise techniques that detect errors with as little resource usage as possible in order to meet the usually strict constraints in space applications. Presented in this paper are two techniques derived from studying the behaviour of the interpolation version of the filter. The first being a parallel prediction technique improves upon DMR in terms of resource usage and offers very close error protection coverage. The second offers a trade-off of resource utilisation against error detection.

Similar content being viewed by others

References

R. Bhakthavatchalu, V.S. Karthika, L. Ramesh, B. Aamani, Design of optimized CIC decimator and interpolator in FPGA, in IEEE International Multi Conference on Automation, Computing, Control, Communication and Compressed Sensing (iMac4s) (2013), pp. 812–817

G. Cardarilli, A. Del Re, D. Giancristofaro, M. Re, L. Simone, Digital modulator architectures for satellite and space applications, in Proceedings of IEEE International Conference on Circuits and Systems for Communicatons (2002), pp. 166–169

R.E. Crochiere, L.R. Rabiner, Optimum FIR digital filter implementations for decimation, interpolation and narrowband filtering. IEEE Trans. Acoust. Speech Signal Process. 23(5), 444–456 (1975)

R.E. Crochiere, L.R. Rabiner, Further considerations in the design of decimators and interpolators. IEEE Trans. Acoust. Speech Signal Process. 24(4), 296–311 (1976)

ECSS-Q-HB-60-02a, ECSS techniques for radiation effects mitigation in ASICs and FPGAs handbook, ECSS Secretariat ESA-ESTEC Requirements & Standards Division, Noordwijk, The Netherlands (2016)

A. Fernandez-Vazquez, G. Jovanovic-Dolecek, Maximally Flat CIC compensation filter: design and multiplierless implementation. IEEE Trans. Circuits. II Syst. Express Briefs 59(2), 113–117 (2012)

F. Giannetti, M. Luise, Digital satellite receiver for wideband multi-rate Ka-band communications. IEEE Trans. Aerosp. Electron. Syst. 43(2), 826–832 (2007)

Eugene B. Hogenauer, An economical class of digital filters for decimation and interpolation. IEEE Trans. Acoust. Speech Signal Process. 29(2), 155–162 (1981)

J. W. Howard, D.M. Hardage, Spacecraft environments, interactions: space radiation and its effects on electronic systems. NASA, Washington, DC, USA, NASA Tech, Rep TP-1999-209373 (1999)

G. Jovanovic-Dolecek, Efficient technique for improving the frequency response of CIC decimation filter, in IEEE International Symposium on Communications and Information Technology (2005)

I. V. McLoughlin et al., Fault tolerance through redundant COTS components for Satellite Application, in Proceedings of the 2003 Joint Fourth International Conference on Information, Communications and Signal Processing, and the Fourth Pacific Rim Conference on Multimedia, Singapore (2003), pp. 296–299

G. Molnar, M. Vucic, Closed-form design of CIC compensators based on maximally flat error correction. IEEE Trans. Circuits Syst. II Express Briefs 58(12), 926–930 (2011)

L.R. Rabiner, R.E. Crochiere, A novel implementation for narrowband FIR digital filters. IEEE Trans. Acoust. Speech Signal Process. 23(5), 457–464 (1975)

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflicts of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gear, K.W., Sánchez-Macián, A., Garcia-Herrero, F. et al. Two Behavioural Error Detection Techniques for the Cascaded Integrator–Comb Interpolation Filter Implemented on FPGA. Circuits Syst Signal Process 39, 5529–5542 (2020). https://doi.org/10.1007/s00034-020-01418-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-020-01418-6