Abstract

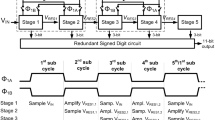

This paper presents a Residue Amplifier (RA) with proposed Common-Mode Feedback (CMFB) scheme for 14-bit 3GSPS pipeline ADC. In order to improve the DC gain and bandwidth, the CMFB circuits in conventional RA are removed to eliminate their negative effect on the output resistance and capacitance. Instead, a small amplifier that only amplifies common-mode signals is connected with the first stage in parallel. Finally, the CMFB loop is constructed with the small amplifier, feedback capacitance and sampling capacitance. The RA is designed with a 28 nm CMOS technology and supplied with single 1.9 V voltage. The post-layout simulation results show that the RA achieves more than 85 dB DC gain and 15 GHz closed-loop bandwidth, which are 4 dB and 2 GHz higher than the conventional one while the power dissipation is reduced by 8.7%.

Similar content being viewed by others

Data availability statement

The datasets supporting the conclusions of this article are included within the article.

References

A. M. A. Ali, "High Speed Data Converters," pp. 262–269, 289–291, IET (2016).

A.M.A. Ali et al., A 14-bit 125 MS/s IF/RF sampling pipelined ADC with 100 dB SFDR and 50 fs jitter. IEEE J. Solid-State Circuits 41(8), 1846–1855 (2006). https://doi.org/10.1109/JSSC.2006.875291

A.M.A. Ali et al., A 12-b 18-GS/s RF sampling ADC with an integrated wideband track-and-hold amplifier and background calibration. IEEE J. Solid-State Circuits 55(12), 3210–3224 (2020). https://doi.org/10.1109/JSSC.2020.3023882

A.M.A. Ali et al., A 16-bit 250-MS/s IF sampling pipelined ADC with background calibration. IEEE J. Solid-State Circuits 45(12), 2602–2612 (2010). https://doi.org/10.1109/JSSC.2010.2073194

A. M. A. Ali et al., "A 14-bit 2.5GS/s and 5GS/s RF Sampling ADC with Background Calibration and Dither," presented at the 2016 IEEE SYMPOSIUM ON VLSI CIRCUITS (VLSI-CIRCUITS), 2016.

Aurangozeb, F. Aryanfar, and M. Hossain, "A Quad Channel 11-bit 1 GS/s 40 mW Collaborative ADC based Enabling Digital Beamforming for 5G Wireless," presented at the 2017 IEEE RADIO FREQUENCY INTEGRATED CIRCUITS SYMPOSIUM (RFIC), 2017.

J. Basu, P. Mandal, Effect of switched-capacitor cmfb on the gain of fully differential op-amp for design of integrators. IEEE International Symposium on Circuits and Systems (ISCAS) 2018, 1–5 (2018). https://doi.org/10.1109/ISCAS.2018.8351346

U. Basumata, A. Mondal, S. Das, H. Rahaman, “Design of Two-Stage Fully-Differential Driver in SAR ADC with Indirect Feedback Compensation Technique,” in, International Symposium on Devices. Circuits and Systems (ISDCS) 2021, 1–5 (2021). https://doi.org/10.1109/ISDCS52006.2021.9397898

B. P. Brandt and J. Lutsky, "A 75-mW, 10-b, 20-MSPS CMOS subranging ADC with 9.5 effective bits at Nyquist," IEEE JOURNAL OF SOLID-STATE CIRCUITS, vol. 34, no. 12, pp. 1788–1795, 1999 DEC 1999.https://doi.org/10.1109/4.808903

H. Fan, A 12-bit 100 MS/s pipelined SAR ADC with addition-only digital error correction. Analog Integrated Circuits Signal Process. 81(1), 325–339 (2014). https://doi.org/10.1007/s10470-014-0389-7

R. Garg et al., A 28-GHz beam-space MIMO RX with spatial filtering and frequency-division multiplexing-based single-wire IF interface. IEEE J. Solid-State Circuits 56(8), 2295–2307 (2021). https://doi.org/10.1109/JSSC.2020.3044089

R. Gray, Oversampled sigma-delta modulation. IEEE Trans. Commun. 35(5), 481–489 (1987). https://doi.org/10.1109/TCOM.1987.1096814

P. Harikumar, J.J. Wikner, A. Alvandpour, A fully-differential OTA in 28 nm UTBB FDSOI CMOS for PGA applications. European Conference on Circuit Theory and Design (ECCTD) 2015, 1–4 (2015). https://doi.org/10.1109/ECCTD.2015.7300114

N. Hiok-Tiaq, R.M. Ziazadeh, D.J. Allstot, A multistage amplifier technique with embedded frequency compensation. IEEE J. Solid-State Circuits 34(3), 339–347 (1999). https://doi.org/10.1109/4.748185

L. Ka Nang, P.K.T. Mok, K. Wing-Hung, J.K.O. Sin, Three-stage large capacitive load amplifier with damping-factor-control frequency compensation. IEEE J. Solid-State Circuits 35(2), 221–230 (2000). https://doi.org/10.1109/4.823447

A.N. Karanicolas, H.S. Lee, K.L. Bacrania, A 15-B 1-MSAMPLE/S digitally self-calibrated pipeline ADC. IEEE J. Solid-State Circuits 28(12), 1207–1215 (1993). https://doi.org/10.1109/4.261994

M. Kashmiri, B. Behroozpour, V. Petkov, K. Wojciechowski, C. Lang, and Ieee, "A 4GS/s 80dB DR Current-Domain Analog Front-End for Phase-Coded Pulse-Compression Direct Time-of-Flight Automotive LiDAR," presented at the 2020 IEEE INTERNATIONAL SOLID- STATE CIRCUITS CONFERENCE (ISSCC), 2020.

H.-J. Kim, 11-bit column-parallel single-slope ADC with first-step half-reference ramping scheme for high-speed CMOS image sensors. IEEE J. Solid-State Circuits 56(7), 2132–2141 (2021). https://doi.org/10.1109/JSSC.2021.3059909

C.C. Lee, M.P. Flynn, A SAR-assisted two-stage pipeline ADC. IEEE J. Solid-State Circuits 46(4), 859–869 (2011). https://doi.org/10.1109/JSSC.2011.2108133

U.K. Moon, B.S. Song, Background digital calibration techniques for pipelined ADC’s. IEEE Trans. Circuits Syst. II-Analog Digit. Signal Process. 44(2), 102–109 (1997). https://doi.org/10.1109/82.554434

S. Padma, S. Das, S. Sen, and C. D. Parikh, "High Performance Operational Amplifier with 90dB Gain in SCL 180nm Technology," in 2020 24th International Symposium on VLSI Design and Test (VDAT), 2020, pp. 1–5.https://doi.org/10.1109/VDAT50263.2020.9190288

J. Wei, C. Zhang, M. Liu, A 11-Bit 1-GS/s 14.9 mW hybrid voltage-time pipelined ADC with gain error calibration. IEEE Trans. Circuits Syst. II Express Briefs 69(3), 799–803 (2022). https://doi.org/10.1109/TCSII.2021.3116591

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interests

The authors have no relevant financial or non-financial interests to disclose.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Huang, C., Gai, W., Zhao, Y. et al. A Residue Amplifier with 85 dB DC Gain and 15 GHz Closed-Loop Bandwidth for 14-Bit 3GSPS Pipeline ADC. Circuits Syst Signal Process 41, 6694–6708 (2022). https://doi.org/10.1007/s00034-022-02121-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-02121-4