Abstract

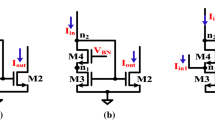

This article aims to design a low-voltage, low-power, bulk-driven OTA with enhanced performance characteristics to surpass existing bulk-driven OTAs. Two adaptively biased class-AB differential pairs in the input core of the amplifier with resistive local common-mode feedback provide two-step amplification with low noise, enhanced dynamic current boosting, and optimum current efficiency. This approach has been studied and tested using the Cadence Spectre simulator with UMC 0.18 µm CMOS technology. The proposed OTA demonstrates noise reduction, DC gain, and slew rate enhancement factors of up to 1.6, 1.31, and 3, respectively, compared to its latest equivalent super class-AB OTA with the same 0.5 µA quiescent currents and transistor’s same aspect ratios under a 0.5 V supply. The proposed OTA achieves the highest figures of merit for small- and large-signal performance (FOMS and FOML) among bulk-driven OTAs studied in the literature, with a DC gain of 118.02 dB, a UGF of 52.02 kHz, a slew rate of 13.69 V/ms, and a total standby current of 2.08 µA for a capacitive load of 5 nF.

Similar content being viewed by others

References

M. Akbari, S.M. Hussein, Y. Hashim, K.-T. Tang, An enhanced input differential pair for low-voltage bulk-driven amplifiers. IEEE Transactions Very Large Scale Integr. (VLSI) Syst., 29(9), 1601–1611, https://doi.org/10.1109/TVLSI.2021.3084695.

E. Cabrera-Bernal, S. Pennisi, A. D. Grasso, A. Torralba and R. G. Carvajal, 0.7-V three-stage class-AB CMOS operational transconductance amplifier. IEEE Transactions Circuits Syst. I: 63(11), 1807–1815 (2016), https://doi.org/10.1109/TCSI.2016.2597440.

J.M. Carrilo, G. Torelli, R. Perez-Aloe, J.F. Duque-Carrillo, 1-V rail-to-rail CMOS OpAmp with improved bulk-driven input. IEEE J. Solid-State Circuits 42(3), 508–517 (2007). https://doi.org/10.1109/JSSC.2006.891717

N. Deo, T. Sharan, T. Dubey, Subthreshold biased enhanced bulk-driven double recycling current mirror OTA Analog Integr. Circuits Signal Process. 105(2), 229–242, https://doi.org/10.1007/s10470-020-01689-8

J.A. Galan, A.J. Lopez-Martin, R.G. Carvajal, J. Ramirez-Angulo, C. Rubia-Marcos, Super class-AB OTAs with adaptive biasing and dynamic output current scaling. IEEE Trans. Circuits Syst. I Regul. Pap. 54(3), 449–433 (2007). https://doi.org/10.1109/TCSI.2006.887639

S. Ghosh, V. Bhadauria, High current efficiency single-stage bulk-driven subthreshold-biased class-AB OTAs with enhanced transconductance and slew rate for large capacitive loads. Analog Integr. Circ. Sig. Process 109(2), 403–433 (2021). https://doi.org/10.1007/s10470-021-01929-5

S. Ghosh, V. Bhadauria, An ultra-low-power bulk-driven subthreshold super class-AB rail-to-rail CMOS OTA with enhanced small and large signal performance suitable for large capacitive loads. Microelectron. J. 115, 105208 (2021). https://doi.org/10.1016/j.mejo.2021.105208

S. Ghosh, V. Bhadauria, An ultra-low-power near rail-to-rail pseudo-differential subthreshold gate-driven OTA with improved small and large signal performances. Analog Integr. Circ. Sig. Process 109(2), 345–366 (2021). https://doi.org/10.1007/s10470-021-01899-8

S. Ghosh, V. Bhadauria, High current efficiency fast transient gain-boosted single-stage bulk-driven OTA with enhanced input stage suitable for heavy capacitive loads. AEU-Int. J. Electron. Commun. (2022). https://doi.org/10.1016/j.aeue.2022.154357

T. Kulej, F. Khateb, Bulk-driven adaptively biased OTA in 0.18 μm CMOS. Electron. Lett. 51(6), 458–460 (2015). https://doi.org/10.1049/el.2014.4437

T. Kulej, F. Khateb, A compact 0.3-V class AB bulk-driven OTA. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 28(1), 224–232 (2020), https://doi.org/10.1109/TVLSI.2019.2937206.

A.J. Lopez-Martin, S. Baswa, J. Ramirez-Angulo, R.G. Carvajal, Low-voltage super class AB CMOS OTA cells with very high slew rate and power efficiency. IEEE J. Solid State Circuits 40(5), 1068–1077 (2005). https://doi.org/10.1109/JSSC.2005.845977

X. Lv, X. Zhao, Y. Wang, D. Jia, Super class AB-AB bulk-driven folded cascode OTA. Integration 63, 196–203 (2018). https://doi.org/10.1016/j.vlsi.2018.07.009

P. Toledo, P. Crovetti, O. Aiello, M. Alioto, Design of digital OTAs with operation down to 0.3 V and nW power for direct harvesting. IEEE Transactions Circuits Syst. I Regul. Papers 68(9), 3693–3706 (2021). https://doi.org/10.1109/TCSI.2021.3089339

H. Veldandi, R.A. Shaik, An ultra-low-voltage bulk-driven analog voltage buffer with rail-to-rail input/output range. Circuits Syst. Signal Process. 36(12), 4886–4907 (2017). https://doi.org/10.1007/s00034-017-0663-x

K.-C. Woo, B.-D. Yang, A 0.25-V rail-to-rail three-stage OTA with an enhanced DC gain. IEEE Transactions Circuits Syst. II Exp. Briefs 67(7), 1179–1183 (2019). https://doi.org/10.1109/TCSII.2019.2935172

Q. Zhigang, A. Tanaka, N. Takaya, H. Yoshizawa, 0.5-V 70-nW rail-to-rail operational amplifier using a cross-coupled output stage. IEEE Transactions Circuits Syst. II Exp. Briefs 63(11), 1009–1013 (2016). https://doi.org/10.1109/TCSII.2016.2539081

Acknowledgements

This work has been performed using the VLSI laboratory resources developed under the Special Manpower Development Program for VLSI design and related software (SMDP-II) project funded by the Department of Information Technology, Government of India, at MNNIT Allahabad, Prayagraj, UP. The authors also thank Mr. Mamidi Nagaraju (Laboratory Engineer) for their cooperation in accessing the tools of the EDA (Cadence Virtuoso IC 6.1.7).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that there is no conflict of interest regarding the publication of this work.

Data Availability

The authors confirm that all data are included within the manuscript.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Ghosh, S. Low-Voltage Super Class-AB Bulk-Driven Single-Stage Subthreshold OTA with Very High DC Gain, Slew Rate, and High Driving Capability. Circuits Syst Signal Process 42, 1279–1292 (2023). https://doi.org/10.1007/s00034-022-02154-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-02154-9