Abstract

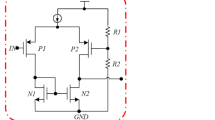

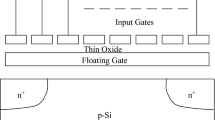

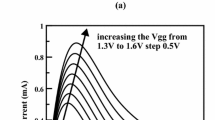

Using MOS-transistors with floating gate (Neuron MOS or νMOS) for building threshold logic is discussed. Two ways of νMOS threshold logic implimention – static and clocked – are under consideration. Methodology of νMOS circuit design is given. Majority voting gate (MVG) is used as an example of threshold gate with worst conditions for getting a large number of inputs. The possibility of implementing a MVG with a certain number of inputs is the possibility of building a threshold gate with a threshold alterable in real time (from OR to AND-function) with the sum of input weights equal to the number of MVG inputs. The maximum number of threshold gate inputs is estimated depending upon the deviations of the elements dimensions and parameters inside the chip. It is shown that it is difficult to implement a static νMOS MVG with a number of inputs more than 10. For the same conditions, the number of inputs of clocked νMOS MVG is as large as many tens. A clocked νMOS threshold gate with alterable in real-time input weights and threshold is proposed. Delay time and chip area for such a circuits are estimated.

Similar content being viewed by others

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Lashevsky, R., Takaara, K. & Souma, M. The efficiency of neuron-MOS transistors in threshold logic. Soft Computing 3, 20–29 (1999). https://doi.org/10.1007/s005000050087

Issue Date:

DOI: https://doi.org/10.1007/s005000050087