Abstract

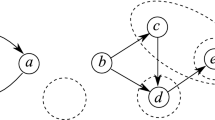

In this paper we present an algorithm for determining satisfiability of general Boolean formulas which are not necessarily in conjunctive normal form. The algorithm extends the well-known Davis–Putnam algorithm to work on Boolean formulas represented using Boolean Expression Diagrams (BEDs). The BED data structure allows the algorithm to take advantage of the built-in reduction rules and the sharing of sub-formulas. Furthermore, it is possible to combine the algorithm with traditional BDD construction (using Bryant’s Apply-procedure). By adjusting a single parameter to the BedSat algorithm, it is possible to control to what extent the algorithm behaves like the Apply-algorithm or like a SAT-solver. Thus, the algorithm can be seen as bridging the gap between standard SAT-solvers and BDDs. We present promising experimental results for 566 non-clausal formulas obtained from the multi-level combinational circuits in the ISCAS’85 benchmark suite and from performing model checking of a shift-and-add multiplier.

Similar content being viewed by others

References

Abdulla, P.A., Bjesse, P., Eén, N.: Symbolic reachability analysis based on SAT solvers. In: Tools and Algorithms for the Construction and Analysis of Systems (TACAS), 2000

Andersen, H.R., Hulgaard, H.: Boolean expression diagrams. Information and Computation. (To appear)

Andersen, H.R., Hulgaard, H.: Boolean expression diagrams. In: IEEE Symposium on Logic in Computer Science (LICS), July 1997

Biere, A., Cimatti, A., Clarke, E.M., Fujita, M., Zhu, Y.: Symbolic model checking using SAT procedures instead of BDDs. In: Proc. ACM/IEEE Design Automation Conference (DAC), 1999

Biere, A., Cimatti, A., Clarke, E.M., Zhu, Y.: Symbolic model checking without BDDs. In: Tools and Algorithms for the Construction and Analysis of Systems (TACAS), Lecture Notes in Computer Science, vol. 1579. Springer-Verlag, 1999

Biere, A., Clarke, E., Raimi, R., Zhu, Y.: Verifying safety properties of a PowerPC microprocessor using symbolic model checking without BDDs. In Computer Aided Verification (CAV), Lecture Notes in Computer Science, vol. 1633. Springer-Verlag, 1999

Bjesse, P.: SAT-based verification without state space traversal. In: Proc. Formal Methods in Computer-Aided Design, Third International Conference, FMCAD’00, Austin, Texas, USA, Lecture Notes in Computer Science, November 2000

Brglez, F., Fujiware, H.: A neutral netlist of 10 combinational benchmarks circuits and a target translator in Fortran. In: Special Session International Symposium on Circuits and Systems (ISCAS), 1985

Bryant, R.E.: Graph-based algorithms for boolean function manipulation. IEEE Transactions on Computers 35(8): 677–691, August 1986

Bryant, R.E.: Binary decision diagrams and beyond: Enabling technologies for formal verification. In: Proc. International Conf. Computer-Aided Design (ICCAD), November 1995, pp. 236–243

Davis, M., Longemann, G., Loveland, D.: A machine program for theorem-proving. Communications of the ACM 5(7): 394–397, July 1962

Davis, M., Putnam, H.: A computing procedure for quantification theory. Journal of the ACM 7: 201–215, 1960

Giunchiglia, E., Sebastiani, R.: Applying the Davis-Putnam procedure to non-clausal formulas. In: Proc. Italian National Conference on Artificial Intelligence, volume 1792 of Lecture Notes in Computer Science, Bologna, Italy. Springer-Verlag, September 1999

Holger Hoos, H., Thomas Stützle. SATLIB – the satisfiability library. http://www.satlib.org

Hulgaard, H., Williams, P.F., Andersen, H.R.: Equivalence checking of combinational circuits using boolean expression diagrams. IEEE Transactions on Computer Aided Design, July 1999

Kunz, W., Pradhan, D.K.: Recursive learning: A new implication technique for efficient solutions to CAD problems – test, verification, optimization. IEEE Transactions on Computer Aided Design 13(9): 1143–1158, September 1994

Marques-Silva, J.P., Sakallah, K.A.: GRASP: A search algorithm for propositional satisfiability. IEEE Transactions on Computers 48: 506–521, 1999

Moskewicz, M., Madigan, C., Zhao, Y., Zhang, L., Malik, S.: Chaff: Engineering an Efficient SAT Solver. In: Proc. of the 39th Design Automation Conference, Las Vegas, June 2001

Mukherjee, R., Jain, J., Takayama, K., Fujita, M., Abraham, J.A., Fussell, D.S.: An Efficient Filter-Based Approach for Combinational Verification. In: Proc. of the Design, Automation and Test in Europe Conference and Exhibition, 1999

Rudell, R.: Dynamic variable ordering for ordered binary decision diagrams. In: Proc. International Conf. Computer-Aided Design (ICCAD), 1993, pp. 42–47

Sebastiani, R.: Applying GSAT to non-clausal formulas. Journal of Artificial Intelligence Research (JAIR), 1: 309–314, January 1994

Selman, B., Levesque, H.J., Mitchell, D.: A new method for solving hard satisfiability problems. In: Rosenbloom, P., Szolovits, P. (eds.) Proc. Tenth National Conference on Artificial Intelligence, Menlo Park, California. American Association for Artificial Intelligence, AAAI Press, 1992, pp. 440–446

Sheeran, M., Stålmarck, G.: A tutorial on Stålmarck’s proof procedure for propositional logic. In: Gopalakrishnan, G., Windley, P.J. (eds.) Proc. Formal Methods in Computer-Aided Design, Second International Conference, FMCAD’98, Palo Alto/CA, USA, Lecture Notes in Computer Science, vol. 1522. November 1998, pp. 82–99

van Eijk, C.A.J.: Sequential equivalence checking without state space traversal. In: Proc. International Conf. on Design Automation and Test of Electronic-based Systems (DATE), 1998

Williams, P.F.: Formal Verification Based on Boolean Expression Diagrams. PhD thesis, Dept. of Information Technology, Technical University of Denmark, Lyngby, Denmark, August 2000. ISBN 87-89112-59-8

Williams, P.F., Biere, A., Clarke, E.M., Gupta, A.: Combining decision diagrams and SAT procedures for efficient symbolic model checking. In: Computer Aided Verification (CAV), Lecture Notes in Computer Science, vol. 1855. Chicago, U.S.A.. Springer-Verlag, July 2000, pp. 124–138

Zhang, H.: SATO: An efficient propositional prover. In: William McCune, editor, Proceedings of the 14th International Conference on Automated deduction, Lecture Notes in Artificial Intelligence, vol. 1249. Berlin, Springer-Verlag, July 1997, pp. 272–275

Author information

Authors and Affiliations

Corresponding authors

Rights and permissions

About this article

Cite this article

Williams, P., Andersen, H. & Hulgaard, H. Satisfiability checking using Boolean Expression Diagrams. Int J Softw Tools Technol Transfer 5, 4–14 (2003). https://doi.org/10.1007/s10009-002-0102-5

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10009-002-0102-5