Abstract

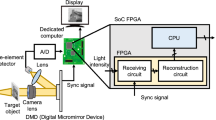

This paper presents field-programmable gate array (FPGA)-based novel forward and backward automatic censored cell algorithms using a Nios II core processor embedded on a Stratix II FPGA programmable device. These algorithms were recently presented for target detection in a nonhomogeneous environment, and they operate in a complementary manner to allow for high-resolution target detection with a time constraint fixed below 0.5 μs. The ACOSD-based constant false alarm rate detector does not require any prior information regarding the background environment and employs statistical analysis to dynamically calculate the threshold at which the ordered cells under investigation are accepted or rejected. The advantages of the proposed system lie in its simplicity and short processing time while maintaining a low development cost. For a reference window of 16 range cells, the experimental results obtained using the Stratix II development kit demonstrate that the proposed architecture works properly with a processing speed of 100 MHz and an overall detector execution time of 0.11 μs for each range cell. The designed hardware, which is an example of system-on-chip architecture, was physically realized in a Stratix II FPGA device, and the results are presented and discussed.

Similar content being viewed by others

References

Barkat M (2005) Signal detection and estimation. Artech House, Norwood

Blake S (1982) OS-CFAR theory for multiple target and nonuniform clutter. IEEE Trans Aerosp Electron Syst 24(6):785–790

Rohling H (1983) Radar CFAR thresholding in clutter and multiple target situations. IEEE Trans Aerosp Electron Syst 19(4):608–621

Meziani HA, Soltani F (2006) Performance analysis of some CFAR detectors in homogenous and non-homogenous Pearson-distributed clutter. Signal Process 86:2115–2122

Larouissi T, Barkat M (2006) Performance analysis of order-statistic CFAR detectors in time diversity systems for partially correlated chi-square targets and multiple target situations. Signal Process 86(7):1617–1631

Mezache A, Soltani F (2007) A novel threshold optimization of ML-CFAR detector in Weibull clutter using fuzzy-neural networks. Signal Process 87:2100–2110

Khalighi MA, Bastani MH (2000) Adaptive CFAR processor for nonhomogenous environment. IEEE Trans Aerosp Electron Syst 36(3):889–897

Saarnisaari H, Henttu P, Juntti M (2005) Iterative multidimensional impulse detectors for communications based on the classical diagnostic methods. IEEE Trans Commun 53(3):395–398

Alshebeili S, Alhumaidi SM, Obied AM, Seddiq YM (2009) FPGA-based implementation of a CFAR processor using Batcher’s sort and LUT arithmetic. In: 4th international design and test workshop (IDT), Riyadh-KSA, pp 1–6

Finn HM, Johnson RS (1968) Adaptive detection mode with threshold control as a function of spatially sampled clutter level estimates. RCA Rev 29:414–463

Sawyers JH, Hansen VG (1980) Detectability loss due to greatest of selection in a cell-averaging CFAR. IEEE Trans Aerosp Electron Syst 16:115–118

Weiss M (1982) Analysis of some modified cell-averaging CFAR processors in multiple target situations. IEEE Trans Aerosp Electron Syst 15(1):102–114

Barkat M, Himonas SD, Varshney PK (1989) CFAR detection for multiple target situations. IEE Proc, F, Radar Signal Process 136(5):193–210

Ravid R, Levanon N (1992) Maximum-likelihood CFAR for Weibull background. IEE Proc, F, Radar Signal Process 139(3):256–264

Anastassopoulos V, Lampropoulos G (1995) Optimal CFAR detection in Weibull clutter. IEEE Trans Aerosp Electron Syst 31(1):52–64

Torres C, Lopez S, Cumplido R (2004) A configurable FPGA-based hardware architecture for adaptive processing of noisy signals for target detection based on constant false alarm rate (CFAR) algorithms. In: Global signal processing conference, Santa Clara, CA, pp 214–218

Bencheikh ML, Magaz B (2008) An efficient FPGA implementation of the OS-CFAR processor. In: International Radar symposium, Wroclaw, pp 1–4

Cumplido R, Uribe C, Del Campo F, Perez R (2010) A versatile hardware architecture for a constant false alarm rat processor based on alinear insertion sorter. Digit Signal Process 20:1733–1747

Ali JK, Yassen ZT, Saed TR (2007) An FPGA-based implementation of CA-CFAR processor. Asian J Inf Technol 6(4):511–514

Alsuwailem AM, Alshebeili SA, Alamar M (2008) Design and implementation of a configurable real-time FPGA-based TM-CFAR processor for radar target detection. J Act Passiv Electron Devices 3(3–4):241–256

Detlefsen J, Siart U, Buchlert J, Wagner M, Winkler V (2004) FPGA-based signal processing of an automotive radar sensor. In: First European Radar conference, Amsterdam, pp 245–248

Almarshad MN, Barkat M, Alshebeili SA (2007) A Monte Carlo simulation for two novel automatic censoring techniques of radar interfering targets in log-normal clutter. Signal Process 88(3):719–732

Alsuwailem AM, Alhowaish MH, Alshebeili SA, Qasim SM (2009) Field programmable gate array-based design and realization of automatic censored cell averaging constant false alarm rate detector based on ordered data variability. IET Circuits Devices Syst 3(1):12–21

Djemal R (2010) A real-time FPGA-based implementation of target detection technique in non-homogenous environment. In: Design and technology of integrated system in nanoscale era (DTIS), Hammamet, Tunisia, pp 1–6

Rosyadi I, Djemal R, Alshebeili S (2009) Design and implementation of real-time automatic censoring system on chip for radar detection. In: World academic of science, engineering and technology (WASET), Penang, Malaysia, pp 318–324

Winter EM, Schlangen MJ, Hendrickson CR Comparisons of target detection in clutter using data from the 1993 FOPEN experiments (Technical report). Naval Command, Control and Ocean Surveillance Center (NCCOSC), RDT&E Division, San Diego, CA 92152-5001

Karmani S, Djemal R, Tourki R (2007) A blind watermarking algorithm implementation for digital images and video. Int J Soft Comput 2(2):292–301

Djemal R, Belwafi K, Kaaniche W, Alshbeili SA (2011) An FPGA-based implementation of HW/SW architecture for CFAR radar target detector. In: International conference on microelectronics (ICM), Tunisia, pp 1–6

Cesario W, Gauthier L, Lyonnard D, Nicolescu G, Jerraya AA (2004) Object-based hardware/software component interconnection model for interface design in system-on-a-chip circuits. J Syst Softw 70:229–244

Atera Corporation (2007) Stratix II architecture, Stratix II device family— Data sheet SII1002-4.3, May 2007

Acknowledgements

The work reported in this paper was supported by the National Plan for Science and Technology (NPST) at King Saud University (project number: ADV-170-2-08).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Djemal, R., Belwafi, K. & Alshebeili, S. An adaptive CFAR embedded system architecture for target detection. Des Autom Embed Syst 17, 109–127 (2013). https://doi.org/10.1007/s10617-013-9121-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10617-013-9121-6