Abstract

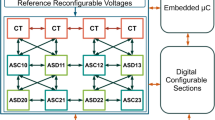

This paper presents the application of the oscillation test methodology as an alternative to test configurable analog blocks of Field Programmable Analog Arrays. The blocks of the device under test are first configured to behave as oscillators. Then, the output frequency and amplitude are observed to obtain the signature of the fault-free circuit. During test, this signature is compared to the actual output signal. Experimental results show the effectiveness of the method in detecting parametric and large deviation faults of the tested components.

Similar content being viewed by others

References

P. Allen and D. Holberg. CMOS Analog Circuit Design, New York: Holt-Rinehart and Winston, 1994.

K. Arabi and B. Kaminska, “Oscillation-Test Strategy for Analog and Mixed-Signal Integrated Circuits,” in 14th VLSI Test Symposium, 1996, pp. 476–482.

K. Arabi and B. Kaminska, “Testing Analog and Mixed-Signal Integrated Circuits Using Oscillation-Test Method,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 16, no. 7, 1997.

K. Arabi and B. Kaminska, “Parametric and Catastrophic Fault Coverage of analog Circuits in Oscillation-Test Methodology,” in Proc. 15th IEEE VLSI Test Symposium, 1997, pp. 166–171.

K. Arabi and B. Kaminska, “Oscillation-Test Methodology for Low-Cost Testing of Active Analog Filters,” IEEE Transactions on Instrumentation and Measurement, vol. 48, no. 4, 1999.

J.V. Calvano, V.C. Alves, M. Lubaszewski, and A.C. Mesquita, “Filters Designed for Testability Wrapped on the Mixed-Signal Test Bus,” in Proc. 20th IEEE VLSI Test Symposium, 2002, pp. 201–206.

A. Chaehoi, Y. Bertrand, L. Latorre, and P. Nouet, “Improving the Efficiency of the Oscillation-based Test Methodology for Parametric Faults,” in IEEE Latin American Test Workshop, 2003.

E. Cota, M. Negreiros, L. Carro, and M. Lubaszewski. “A New Adaptive Analog Test and Diagnosis System,” IEEE Transactions on Instrumentation and Measurement, vol. 49, no. 2, pp. 223–227, 2000.

G. Gielen, Z. Wang, and W. Sansen, “Fault Detection and Input Stimulus Determination for the Testing of Analog Integrated Circuits Based on Power-Supply Current Monitoring,” in Proc. IEEE ICCAD, 1994, pp. 495–498.

G. Huertas, D. Vázquez, E.J. Peralias, A. Rueda, and J.L. Huertas, “Testing Mixed-Signal Cores: A Practical Oscillation-Based Test in an Analog Macrocell,” IEEE Design & Test of Computers, vol. 19, no. 6, pp. 64–72, 2002.

G. Huertas, D. Vázquez, E.J. Peralias, A. Rueda, and J. L. Huertas, “Practical Oscillation-Based Test of Integrated Filters,” IEEE Design & Test of Computers, vol. 19, no. 6, 2002.

G. Huertas, D. Vázquez, A. Rueda, and J.L. Huertas, “Effective Oscillation-Based Test for application to a DTMF Filter Bank,” in Proc. IEEE International Test Conference, Sept. 1999, pp. 549–555.

ispPAC Handbook, “Programmable Analog Circuits,” Lattice Semiconductor Corporation, 2000.

M. Lubaszewski, S. Mir, and L. Pulz, “ABILBO: Analog BuILt-in Block Observer,” in IEEE/ACM International Conference on Computer-Aided Design, 1996, pp. 600–603.

S. Mir, M. Lubaszewski, and B. Courtois, “Fault-based ATPG for Linear Analog Circuits with Minimal Size Multifrequency Test Sets,” in JETTA, Special Issue on Mixed-Signal Testing, Kluwer, vol. 9, 1996.

P. Nigh and W. Maly, “Test Generation for Current Testing,” IEEE Design and Test of Computers, vol. 7, no. 2, pp. 26–38, 1990.

C.L. Wey, “Built-in Self-Test Structure for Analog Circuit Fault Diagnosis,” IEEE Trans. Instrum. Meas., vol. 39, no. 3, pp. 517–521, 1990.

Author information

Authors and Affiliations

Corresponding author

Additional information

Tiago Roberto Balen was born in Erechim, Brazil, in 1979. He received the Electrical Engineering degree from the Universidade Federal do Rio Grande do Sul (UFRGS), Porto Alegre, Brazil in 2004. At present, he is M.Sc. student in the Electrical Engineering Department and works in the Prototyping and Test Laboratory at UFRGS. His research interests include analog and mixed-signal design and test, built-in self-test and design-for-testability. He has published papers on FPAA testing in important conferences, such as the VLSI Test Symposium (VTS) and the International Test Conference (ITC).

Antonio Andrade, Jr., received the Electrical Engineering degree from the Universidade Federal da Bahia (UFBA), Salvador, Brazil, in 2003, and is currently pursuing the M.Sc. degree at Universidade Federal do Rio Grande do Sul (UFRGS), Porto Alegre, Brazil. His experience as a researcher includes the design of a temperature controller using thermo-resistive sensors and FPGA prototyping, at the Instrumentation Laboratory in UFBA, in 2001, a 2-month scholarship from Laboratorio Nacional de Luz Sincrotron (LNLS), Campinas, Brazil, in 2002, and 2 years as a graduate student at the Prototyping and Test Laboratory, at UFRGS. His primary research topics include Mixed-Signal Circuit and Systems Testing as well as fast system prototyping in platforms as FPGAs and FPAAs, having published papers in important conferences, such as the VLSI Test Symposium (VTS) and International Test Conference (ITC), in the field of FPAA testing.

Florence Azaïs received the Ph.D. degree in electrical engineering from the University of Montpellier, France in 1996. She is currently working in the Microelectronics department of the Laboratory of Computer Science, Robotics and Microelectronics of Montpellier (LIRMM) as a researcher of the National Council of Scientific Research (CNRS). Since 1993, she has been interested in the general domain of test and reliability of integrated circuits and systems. Her main research interests include fault modeling, analog and mixed-signal circuit testing, MEMS testing, reliability and failure analysis of integrated systems. She has authored or co-authored over 80 international papers on these topics. She also served as a member of the Program Committee of several international conferences (DATE, ICCD, ETS, IMSTW, LATW).

Marcelo Lubaszewski received the Electrical Engineering and M.Sc. degrees from the Universidade Federal do Rio Grande do Sul (UFRGS), Porto Alegre, Brazil, in 1986 and 1990, respectively. In 1994, he received the Ph.D. degree from the Institut National Polytechnique de Grenoble (INPG), France. In 2001, he joined the Laboratoire d’Informatique, Robotique et Microélectronique de Montpellier in France as an Invited Researcher for 3 months and, in 2004, the Instituto de Microelectrónica de Sevilla (IMSE) in Spain for 1 year. He is currently with UFRGS, where he has been an Associate Professor since 1990. His primary research interests include design and test of mixed-signal, micro-electro-mechanical and core-based systems, self-checking and fault-tolerant architectures, and computer-aided testing. He has published over 150 papers in international journals and conferences on these topics. Dr. Lubaszewski has served as the general chair or program chair of the Symposium on Integrated Circuits and Systems Design (SBCCI) and of the Latin American Test Workshop (LATW), and as a member of the Organizing or the Program Committee of the VLSI Conference, the International Mixed-Signals Testing Workshop, the Asian Test Symposium, the European Design and Test Conference, the Design of Complex Integrated Systems Conference, the European Test Symposium and the GHz/Gbps Test Workshop. He has also served as a Guest Editor of the Journal of Electronic Testing: Theory and Applications and as an Associate Editor of the Design and Test of Computers Magazine.

Michel Renovell is head of the Microelectronics Department at LIRMM (Laboratory of Computer Science, Automation and Microelectronics of Montpellier). His research interests include: Fault modeling, Analog testing and FPGA testing. He is Vice-Chair of the IEEE TTTC (Test Technology Technical Committee). He is a member of the editorial board of JETTA and the editorial board of IEEE Design & Test. Michel has been General Chair of the International Mixed Signal Testing Workshop IMSTW2000, the Field Programmable Logic Conference FPL2002 and the European Test Symposium ETS2004.

Rights and permissions

About this article

Cite this article

Balen, T.R., Andrade, A.Q., AzaÏs, F. et al. Applying the Oscillation Test Strategy to FPAA’s Configurable Analog Blocks. J Electron Test 21, 135–146 (2005). https://doi.org/10.1007/s10836-005-6143-4

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/s10836-005-6143-4