Abstract

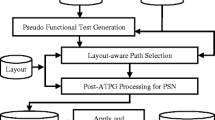

Power supply noise and crosstalk are the two major noise sources that are pattern dependent and negatively impact signal integrity in digital integrated circuits. These noise sources play a greater role in sub-65nm technologies and may cause timing failures and reliability problems in a design; thus must be carefully taken into consideration during test pattern generation and validation. In this paper, we propose a novel method to evaluate path-delay fault test patterns in terms of their ability to cause excess delay on targeted critical paths. It quantifies the noises with a pattern quality value (Q) using the activated aggressor gates and nets information. The proposed method offers design engineers a quick approach to evaluate the critical paths in static timing analysis (STA) and silicon to improve timing margin strategies. By evaluating the failed test pattern, the proposed method can be used to help identify the root cause during failure analysis. Simulation results demonstrate the efficiency and effectiveness of the pattern grading procedure.

Similar content being viewed by others

References

Ahmed N, Tehranipoor M, Jayaram V (2007) Supply voltage noise aware ATPG for transition delay faults. In: Proc. VLSI test symposium (VTS’07), pp 179–186

Belete D, Razdan A, Schwarz W, Raina R, Hawkins C, Morehead J (2002) Use of DFT techniques in speed grading a 1GHz+ microprocessor. In: Proc. of int. test conf. (ITC’02), pp 1111–1119

Chen W, Gupta S, Breuer M (1999) Test generation for crosstalk-induced delay in integrated circuits. In: Proc. int. test conf. (ITC’99), pp 191–200

Chen W, Gupta S, Breuer M (2000) Test generation for crosstalk-induced faults: framework and computational results. In: Proc. Asian test conf. (ATS’00), pp 305–310

Chen W, Gupta SK, Breuer MA (2002) Analytical models for crosstalk excitation and propagation in VLSI circuits. In: IEEE Trans CAD 21(10):1117–1131

Cuviello M, Dey S, Bai X, Zhao Y (1999) Fault modeling and simulation for crosstalk in system-on-chip interconnects. In: Proc. int. conf. computer-aided design (ICCD’99), pp 297–303

Krstic A, Jiang YM, Cheng KT (2001) pattern generation for delay testing and dynamic timing analysis considering power-supply noise effects. IEEE Trans CAD 20(3):416–425

Krstic A, Liou J, Jiang Y, Cheng KT (2001) Delay testing considering crosstalk induced effects. In: Proc. int. test conf. (ITC’01), pp 558–567

Lee J, Tehranipoor M (2008) A novel pattern generation framework for inducing maximum crosstalk effects on delay-sentive paths. In: Proc. int. test conf. (ITC’08)

Lee J, Narayan S, Tehranipoor M (2008) Layout-aware, IR-drop tolerant transition fault pattern generation. In: Proc. design, automation, and test in Europe (DATE’08), pp 1172–1177

Liu X, Hsiao MS (2004) On identifying functionally untestable transition faults. In: IEEE intl. high-level design validation and test workshop, pp 121–126

Ma J, Lee J, Tehranipoor M (2009) Layout-aware pattern generation for maximizing supply noise effects on critical paths. In: Proc. IEEE VLSI test symposium (VTS’09), pp 221–226

Ma J, Ahmed N, Tehranipoor M (2011) Low-cost diagnostic pattern generation and evaluation procedures for noise-related failures. In: IEEE VLSI test symposium (VTS), pp 309–314

Peng K, Thibodeau J, Yilmaz M, Chakrabarty K, Tehranipoor M (2010) A novel hybrid method for SDD pattern grading and selection. In: Proc. IEEE VLSI test symposium (VTS’10), pp 45–50

Sinha A, Gupta SK, Breuer MA (2002) Validation and test issues related to noise induced by parasitic inductances of VLSI interconnects. IEEE Trans Adv Packaging 25()3:329–339

Sinha A, Gupta S, Breuer M (2003) An enchanced test generator for capacitance induced crosstalk delay faults. In: Proc. Asian test conf. (ATS’03), pp 174–177

Synopsys Inc. (2005) User manuals for synopsys toolset version 2005.09. Synopsys Inc.

Tehranipour M, Ahmed N, Nourani M (2003) Multiple transition model and enhanced boundaryscan architecture to test interconnects for signal integrity. In: Proc. int. conf. computer design (ICCD’03)

Tehranipour M, Ahmed N, Nourani M (2003) Testing SoC interconnects for signal integrity using boundary scan. In: proc. IEEE VLSI test symposium (VTS’03), Napa, CA, pp 158–163

Visweswariah C et al (2006) First-order incremental block-based statistical timing analysis. IEEE Trans CAD 25(10):2170–2180

Wang L-C, Liou J-J, Cheng K-T (2004) Critical path selection for delay fault testing based upon a statistical timing model. IEEE Trans CAD 23(11):1550–1565

Yilmaz M, Chakrabarty K, Tehranipoor M (2008) Test-pattern grading and pattern selection for small-delay defects. In: Proc. IEEE VLSI test symposium (VTS’08), pp 233–239

Zeng J, Abadir MS, Vandling G, Wang L-C, Karako S, Abraham JA (2004) On correlating structural tests with functional tests for speed binning of high performance design. In: Proc. of int. test conf. (ITC’04), pp 31–37

Zhang Z, Reddy SM, Pomeranz I (2005) On generating pseudo-functional delay fault tests for scan designs. In: IEEE intl. symposium on defect and fault tolerance in VLSI systems, pp 398–405

Zhao S, Roy K (2000) Estimation of switching noise on power supply lines in deep sub-micro CMOS circuits. In: Proc. thirteenth int. conf. on VLSI design, pp 168–173

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: A.D. Singh

This work was supported in part by National Science Foundation grant CCF-0811632.

Rights and permissions

About this article

Cite this article

Ma, J., Tehranipoor, M. & Girard, P. A Layout-Aware Pattern Grading Procedure for Critical Paths Considering Power Supply Noise and Crosstalk. J Electron Test 28, 201–214 (2012). https://doi.org/10.1007/s10836-011-5268-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-011-5268-x