Abstract

When testing resources are severely limited, special attention should be paid to critical faults/defects so that important or frequent field failures arising from test escapes can be minimized. We present a new algorithm to optimize test sets aimed at significantly reducing the criticality of test escapes—especially for very short test sets that may be applied in the field. The algorithm proposes an exponential-based test set quality model to evaluate the criticality of potential undetected defects and develops a programming model to search for a test set that effectively reduces this criticality.

Similar content being viewed by others

References

Biswas A, Racunas P, Cheveresan R, Emer J, Mukherjee SS, Rangan R (2005) Computing architectural vulnerability factors for address-based structures. Proc. 32nd international symposium on computer architecture, 4–8 June 2005, pp 532–543

Breuer MA (2004) Intelligible test techniques to support error tolerance. 13th Asian test symposium, 2004, pp 386–393

Breuer MA, Gupta S, Mak TM (2004) Defect and error tolerance in the presence of massive numbers of defects. IEEE design and test of computers, May–Jun 2004, pp 216–227

Butler KM, Mercer MR (1991) Quantifying: Non-target defect detection by target fault test sets. In: Europe test symposium, 1991

Chong IS, Ortega A (2005) Hardware testing for error tolerant multimedia compression based on linear transforms. 20th IEEE international symposium on defect and fault tolerance in VLSI systems, 3–5 Oct 2005, pp 523–531

Chung H, Ortega A (2005) Analysis and testing for error tolerant motion estimation. 20th IEEE international symposium on defect and fault tolerance in VLSI systems, 3–5 Oct 2005, pp 514–522

Dworak J (2007) Which defects are most critical? Optimizing test sets to minimize failures due to test escapes. Proc. IEEE international test conference, 23–25 Oct 2007, pp 1–10

Dworak J, Dorsey D, Wang A, Mercer MR (2004) Excitation, observation, and ELF-MD: optimization criteria for high quality test sets. Proc. 22nd IEEE VLSI test symposium, 25–29 Apr 2004, pp 9–15

Dworak J, Wicker JD, Lee S, Grimaila MR, Butler KM, Stewart B, Wang L-C, Mercer MR (2001) Defect-oriented testing and defective-part-level prediction. IEEE Des Test Comput 18(No. 1):31–41

Grimaila MR, Lee S, Dworak J, Butler KM, Stewart F, Balachandran H, Houchins B, Mathur V, Park J, Wang L-C, Mercer MR (1999) REDO—Random Excitation and Deterministic Observation—first commercial experiment. Proc. 17th VLSI test symposium, 25–29 Apr 1999, pp 268–274

Hsieh T-Y, Lee K-J, Breuer MA (2006) An error-oriented test methodology to improve yield with error-tolerance. Proc. 24th VLSI test symposium, 30 Apr–4 May 2006, pp 130–135

Hsieh T-Y, Lee K-J, Breuer MA (2008) An error rate based test methodology to support error-tolerance. IEEE Trans Reliab 57(1):204–214

Huang I-D, Gupta SK (2007) On generating vectors that invoke high circuit delays – delay testing and dynamic timing analysis. 16th Asian test symposium, 8–11 Oct 2007, pp 485–492

Jiang Z, Gupta SK (2002) An ATPG for threshold testing: Obtaining acceptable yield in future processes. Proc. international test conference, 7–10 Oct 2002, pp 824–833

Jiang Z, Gupta SK (2009) Threshold testing: improving yield for nanoscale VLSI. IEEE Trans Comput Aided Des Integr Circ Syst 28(No.12):1883–1895

Kapur R, Park J, Mercer MR (1992) All tests for A fault are not equally valuable for defect detection. Proc. international test conference, 20–24 Sep 1992, pp 762–769

Lee K-J, Hsieh T-Y, Breuer MA (2005) A novel test methodology based on error-rate to support error tolerance. Proc. international test conference, 8 Nov 2005, pp 1136–1144

Ma SC, Franco P, McCluskey EJ (1995) An experimental chip to evaluate test techniques experiment results. Proc. international test conference, 21–25 Oct 1995, pp 663–672

Mukherjee S, Weaver CT, Emer J, Reinhardt SK (2003) Measuring architectural vulnerability factors. IEEE Micro 23(No. 6):70–75

Nowroth D, Polian I, Becker B (2008) A study of cognitive resilience in a JPEG compressor. IEEE international conference on dependable systems and networks with FTCS and DCC, 24–27 June 2008, pp 32–41

Pan Z, Breuer MA (2007) Estimating error rate in defective logic using signature analysis. IEEE Trans Comput 56(5):650–661

Polian I, Nowroth D, Becker B (2007) Identification of critical errors in imaging applications. 13th IEEE international on-line testing symposium, 8–11 July 2007, pp 201–202

Polian I, Pomeranz I, Reddy SM, Becker B (2004) Exact computation of maximally dominating faults and its application to n-detection tests for full-scan circuits. Proc IEE Comput Digit Tech 151(3):235–244

Pomeranz I, Reddy S (2001) On the use of fault dominance in n-detection test generation. Proc. 19th IEEE VLSI test symposium, 29 Apr–3 May 2001, pp 352–357

Rearick J (2001) Too much delay fault coverage is a bad thing. Proc. international test conference, 30 Oct–1 Nov 2001, pp 624–633

Shahidi S, Gupta SK (2006) Estimating error rate during self-test via one’s counting. IEEE international test conference, Oct 2006, pp 1–9

Shahidi S, Gupta SK (2008) Multi-vector tests: A path to perfect error-rate testing. Design, Automation and Test in Europe, 10–14 Mar 2008, pp 1178–1183

Shahidi S, Sandeep KG (2007) A theory of error-rate testing. International conference on computer design, 1–4 Oct 2007, pp 432–445

Shi Y, Dworak J (2008) Efficient determination of fault criticality for manufacturing test set optimization. IEEE international symposium on defect and fault tolerance of VLSI systems, 1–3 Oct 2008, pp 403–411

Shi Y, Hu W-C, Dworak J (2010) Too many faults, too little time: on creating test sets for enhanced detection of highly critical faults and defects. 28th IEEE VLSI test symposium, 19–22 Apr 2010, pp 319–324

Tian Y, Grimaila MR, Shi W, Mercer MR (2005) An optimal test pattern selection method to improve the defect coverage. Proc. IEEE international test conference, Nov 2005, pp 770

Wang Z, Chakrabarty K (2006) An efficient test pattern selection method for improving defect coverage with reduced test data volume and test application time. 15th Asian test symposium, Nov 2006, pp 333–338

Wang L-C, Mercer MR, Williams TW (1995) On the decline of testing efficiency as the fault coverage approaches 1 W%. In: VLSI test symposium, 1995

Wang L-C, Mercer MR, Williams TW (1995) Reducing defective part level via unbiased test set. In: Design and test conference, 1995, pp 294–302

Wang L-C, Mercer MR, Williams TW (1995) On efficiently and reliably achieving low defective part levels. In: International test conference, 1995, pp 616–625

Acknowledgments

This work was supported in part by NSF grants CCF-1110290 and CCF-1061164.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: M. Violante

Rights and permissions

About this article

Cite this article

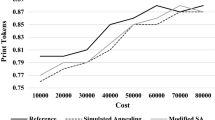

Shi, Y., Dworak, J. A Simulated Annealing Inspired Test Optimization Method for Enhanced Detection of Highly Critical Faults and Defects. J Electron Test 29, 275–288 (2013). https://doi.org/10.1007/s10836-013-5357-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-013-5357-0