Abstract

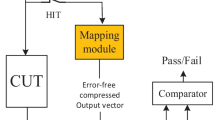

This paper describes the implementation of a shift-register based Built-In Self-Test (BIST) architecture for FPGA global interconnection resources testing. Through this, it is possible to configure FPGA resources that need to be tested in order to obtain high reliability FPGA-based systems. The proposed BIST approach takes advantage of FPGA low-level resources in order to generate cyclic test patterns, analyse testing response and store test results in a simple way. Additionally, the same BIST configuration set is capable of diagnosing the tested interconnection resources with no additional configurations thereby reducing time requirements. This paper presents the proposed BIST architecture and its diagnosis scheme, its implementation on a Xilinx FPGA, and experimental results.

Similar content being viewed by others

References

Abdul-Aziz M, Tahoori M (2010) Soft error reliability aware placement and routing for FPGAs. In: Proceedings of International Test Conference, pp 1–9

Abramovici M, Stroud C (2001) BIST-based test and diagnosis of FPGA logic blocks. IEEE Trans Very Large Scale Integr Syst 9(1):159–172

Altera Corporation (2003) An analytical review of FPGA logic efficiency in Stratix, Virtex-II, Virtex-II Pro Devices. http://www.altera.com/literature/wp/wp_stx_logic_efficiency.pdf

Dixon BE (2008) Built-in self-test of the programmable interconnect in field programmable gate arrays. M.S. thesis, Auburn University

Elshafey K (2004) On-line diagnosis of interconnect faults in FPGA-based systems. In: Proceedings of 16th International Conference on Microelectronics, pp 396–399

Farooq U, Marrakchi Z, Mehrez H (2012) FPGA architectures: An overview. In: Tree-based Heterogeneous FPGA Architectures. Springer, New York, pp 7–48

Peng YL, Kwai DM, Chou YF, Wu CW (2014) Application-independent testing of 3-D field programmable gate array interconnect faults. IEEE Trans Very Large Scale Integr Syst 22(2):207–219

Rehman SU, Benabdenbi M, Anghel L (2013) BIST for logic and local interconnect resources in a novel mesh of cluster FPGA. In: Proceedings of IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems, pp 296–301

Rehman SU, Benabdenbi M, Anghel L (2014) Test and diagnosis of FPGA cluster using partial reconfiguration. In: Proceedings of 10th Conference on Ph.D. Research in Microelectronics and Electronics, pp 1–4

Ruan A, Yang J, Wan L, Jie B, Tian Z (2013) Insight into a generic interconnect resource model for xilinx virtex and spartan series FPGAs. IEEE Trans Circ Syst II: Express Briefs 60(11):801–805

Souza CP, De Assis FM, Freire RCS (2010) A new architecture of test response analyzer based on the Berlekamp-Massey Algorithm for BIST. IEEE Trans Instrum Meas 59(12):3168–3173

Stroud C, Wijesuriya S, Hamilton C, Abramovici M (1998) Built-in self-test of FPGA interconnect. In: Proceedings of International Test Conference, pp 404–411

Xilinx Inc (2011) Spartan 3e user guide ug331, xilinx inc. http://www.xilinx.com/support/documentation/user_guides/ug331.pdf

Xilinx Inc (2013) Spartan 3e datasheet ds312. http://www.xilinx.com/support/documentation/data_sheets/ds312.pdf

Yao J, Dixon B, Stroud C, Nelson V (2009) System-level built-in self-test of global routing resources in Virtex-4 FPGAs. In: Proceedings of 41st Southeastern Symposium on System Theory, pp 29–32

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: V. D. Agrawal

Rights and permissions

About this article

Cite this article

Pereira, I.G., Dias, L.A. & de Souza, C.P. A Shift-Register Based BIST Architecture for FPGA Global Interconnect Testing and Diagnosis. J Electron Test 31, 207–215 (2015). https://doi.org/10.1007/s10836-015-5515-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-015-5515-7