Abstract

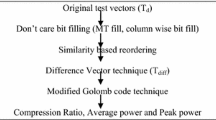

A power efficient System-on-a-Chip test data compression method using alternating statistical run-length coding is proposed. To effectively reduce test power dissipation, the test set is firstly preprocessed by 2D reordering scheme. To further improve the compression ratio, 4 m partitioning of the runs and a smart filling of the don’t care bits provide the nice results, and alternating statistical run-length coding scheme is developed to encode the preprocessed test set. In addition, a simple decoder is obtained which consumed a little area overhead. The benchmark circuits verify the proposed power efficient coding method well. Experimental results show it obtains a high compression ratio, low scan-in test power dissipation and little extra area overhead during System-on-a-Chip scan testing.

Similar content being viewed by others

References

Chandra A, Chakrabarty K (2002) Low-power scan testing and test data compression for system-on-a-chip. IEEE Trans Comput Aided Des 21(5):597–604

Chandra A, Chakrabarty K (2002) Reduction of SoC test data volume, scan power and testing time using alternating run-length codes. In: 39th Design Automation Conference, pp 673–678

Chandra A, Chakrabarty K (2003) Test data compression and test resource partitioning for system-on-a-chip using frequency-directed run-length (FDR) codes. IEEE Trans Comput 52(8):1076–1088

Chandra A, Chakrabarty K (2003) A unified approach to reduce SOC test data volume, scan power and testing time. IEEE Trans Comput Aided Des 22(3):352–362

Czysz D, Kassab M, Lin X, Mrugalski G, Rajski J, Ticker J (2009) Low-power scan operation in test compression environment. IEEE Trans Comput Aided Des 28(11):1742–1755

El-Maleh AH (2008) Test data compression for system-on-a-chip using extended frequency-directed run-length code. Electron Lett 2(3):155–163

El-Maleh AH (2008) Efficient test compression technique based on block merging. IET Comput Digit Tech 2(5):327–355

Gonciari PT, Al-Hashimi BM, Nicolici N Improving compression ratio, area overhead, and test application time for system-on-a-chip test datacompression. Proceedings 2002 Design, Automation and Test in Europe Conference and Exhibition, pp 604–611

Gonciari PT, Al-Hashimi BM, Nicolici N (2003) Variable-length input Huffman coding for system-on-a-chip test. IEEE Trans Comput Aided Des 22(6):783–796

Haiying Y, Guo K, Xun S, Jiaping M, Hongying S (2015) A power efficient BIST TPG method on don’t care Bit based 2-D adjusting and hamming distance based 2-D reordering. J Electron Test 31(1):43–52

Jas A, Ghosh-Dastidar J, Ng M-E, Touba NA (2003) An efficient test vector compression scheme using selective Huffman coding. IEEE Trans Comput Aided Des 22(6):797–806

Kavousianos X, Kalligeros E, Nikolos D (2007) Optimal selective Huffman coding for test-data compression. IEEE Trans Comput 56(8):1146–1152

Lee L-J (2012) 2n-pattern run-length for test data compression. IEEE Trans Comput Aided Des 31(4):644–648

Lee J, Touba NA (2007) LFSR-reseeding scheme achieving low-power dissipation during test. IEEE Trans Comput Aided Des 26(2):396–401

Nourani M, Tehranipour MH (2005) RL-huffman encoding for test compression and power reduction in scan applications. ACM Trans Des Autom Electron 10(1):91–115

Rosinger P, Al-Hashimi BA, Nicolici N (2004) Scan architecture with mutually exclusive scan segment activation for shift- and capture-power reduction. IEEE Trans Comput Aided Des 23(7):1142–1153

Rosinger P, Gonciari PT, Al-Hashimi BM, Nicolici N (2001) Simultaneous reduction in volume of test data and power dissipationfor systems-on-a-chip. Electron Lett 37(24):1434–1436

Ruan X, Rajendra K (2006) An efficient data-independent technique for compressing test vectors in systems-on-a-chip, Emerging VLSI Technologies and Architectures. In: IEEE Computer Society Annual Symposium

Sivanantham S, Padmavathy M, Gopakumar G et al (2014) Enhancement of test data compression with multistage encoding. Integration 47(4):499–509

Tehranipoor M, Nourani M, Chakrabarty K (2005) Nine-coded compression technique for testing embedded cores in SoCs. IEEE Trans VLSI Syst 13(6):719–731

Tenentes V, Kavousianos X (2013) High-quality statistical test compression with narrow ATE interface. IEEE Trans Comput Aided Des 32(9):1369–1382

Touba NA (2006) Survey of test vector compression techniques. IEEE Des Test 23(4):294–303

Tseng W-D, Lee L-J (2010) Test data compression using multi-dimensional pattern run-length codes. J Electron Test 26(3):393–400

Wu T-B, Liu H-Z, Liu P-X (2013) Efficient test compression technique for SoC based on block merging and eight coding. J Electron Test 29(6):849–859

Yuan H, Mei J, Song H, Guo K (2014) Test data compression for system-on-a-chip using count compatible pattern run-length coding. J Electron Test 30(2):237–242

Yuan HY, Mei JP, Sun X, Cheng KT, Guo K (2015) A power efficient test data compression method on count compatible PRL coding. J Circuit Syst Comput 24(6):1550084

Zhan W, El-Maleh A (2012) A new collaborative scheme of test vector compression based on equal-run-length coding (ERLC). Integration 45(1):91–98

Acknowledgments

This research work was supported by the National Natural Science Foundation of China (61001049, 61372149 and 61370189) and Scholarship sponsored by China Scholarship Council [2013] 3018.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: N. A. Touba

Rights and permissions

About this article

Cite this article

Yuan, H., Guo, K., Sun, X. et al. A Power Efficient Test Data Compression Method for SoC using Alternating Statistical Run-Length Coding. J Electron Test 32, 59–68 (2016). https://doi.org/10.1007/s10836-016-5562-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-016-5562-8