Abstract

A triple modular redundancy SRAM was designed as the embedded high-speed memory for a radiation-tolerant ARM processor with ST Microelectronics 28-nm FDSOI technology. The single event upset (SEU) cross-section of the SRAM was tested by using heavy ions with the linear energy transfer of 15.0 meV.cm2.mg−1 in both non-TMR and TMR modes with different accumulated fluence. The SRAM cell was also simulated by using Cogenda TCAD simulation suite and the cross section was calculated by using analytic method. The results showed the cross-section is around 2E-10 cm2/bit in non-TMR mode, and in TMR mode it varied from one to several orders lower than the non-TMR mode according to the specific accumulated fluence. As a scrubbing circuit was designed to reduce the accumulated number of SEUs in the SRAM, the Failure In Time (FIT) rate at sea level in New York City could be as low as 8E-11, which is robust enough for the whole circuit.

Similar content being viewed by others

References

Chen CH, Knag P, Zhang ZY (2014) Characterization of heavy ion-induced single-event effects in 65 nm bulk CMOS ASIC test chips. IEEE Trans Nucl Sci 61(5):2694–2701

Dodd PE, Massengill LW (2003) Basic mechanisms and modeling of single-event upset in digital microelectronics. IEEE Trans Nucl Sci 50(3):583–602

Wu Q, Li YQ, Chen L, He AL, Guo G, Baeg SH, Wang HB, Liu R, Li LX, Wen SJ, Wong R, Allman S, Fung R (2015) Supply voltage dependence of heavy ion induced SEEs on 65 nm CMOS bulk SRAMs. IEEE Trans Nucl Sci 62(4):1898–1904

Bhuva BL, Wen SJ, Wong R, Garza A (2003) Single-Event Effects on SSD controllers. IEEE Trans Nucl Sci 50(3):583–602

Dodd PE, Shaneyfelt MR, Schwank JR, Felix JA (2010) Current and Future Challenges in Radiation Effects on CMOS Electronics. IEEE Trans Nucl Sci 57(4):1747–1763

Schwank JR, Ferlet-Cavrois V, Shaneyfelt MR, Paillet P, Dodd PE (2003) Radiation effects in SOI technologies. IEEE Trans Nucl Sci 50(3):522–538

Gasiot G, Soussan D, Glorieux M, Bottoni C, Roche P (2014) SER/SEL performances of SRAMs in UTBB FDSOI 28-and comparisons with PDSOI and BULK counterparts. In: Proc IEEE Int Reliab Phys Symp (IPRS), SE.6.1 - SE.6.5.

Dutta A, Touba NA (2007) Multiple Bit Upset Tolerant Memory Using a Selective Cycle Avoidance Based SEC-DED-DAEC Code. In: Proc 25th IEEE VLSI Test Symp (VTS’07), 349–354.

Vaillant V, Rivert F (2017) An Analog RF Fully Differential Common Mode Controlled Delay Line in 28-nm FDSOI Technology. In: Proc Symp Int Circuits Syst Design (SBCCI), 120–124.

Gasiot G, Soussan D, Glorieux M, Bottoni C, Roche P (2014) SER/SEL performances of SRAMs in UTBB FDSOI28 and comparisons with PDSOI and BULK counterparts. In Proc IEEE Int Reliab Phys Symp (IPRS), SE.6.1 - SE.6.5.

Wang HB, Chen L, Liu R, Li YQ, Kauppila JS, Bhuva BL, Lilja K, Wen SJ, Wong R, Fung R, Baeg S (2016) An Area Efficient Stacked Latch Design Tolerant to SEU in 28 nm FDSOI Technology. IEEE Trans Nucl Sci 63(6):3003–3009

Wang HB, Kauppila JS, Lilja K, Bounasser M, Chen L, Newton M, Li YQ, Liu R, Bhuva BL, Wen SJ, Wong R, Fung R, Baeg S, Massengill LW (2017) Evaluation of SEU Performance of 28-nm FDSOI Flip-Flop Designs. IEEE Trans Nucl Sci 64(1):367–373

Rollins N, Wirthlin M, Caffrey M, Graham P (2003) Evaluating TMR techniques in the presence of single event upsets. In Proceedings of the 6th Annual International Conference on Military and Aerospace Programmable Logic Devices (MAPLD), P63.

Carmichael C (2001) Triple module redundancy design techniques for Virtex FPGAs. Available: http://ebook.pldworld.com/semiconductors/Xilinx/DataSource%20CD-ROM/Rev.8%20(Q1-2003)/appnotes/xapp197.pdf2003)/appnotes/xappn197.pdf

Loveless TD, Jagannathan S, Reece T, Chetia J, Bhuva BL, McCurdy MW, Massengill LW (2011) Neutron- and Proton-Induced Single Event Upsets for D- and DICE-Flip/Flop Designs at a 40 nm Technology Node. IEEE Trans Nucl Sci 58(3):1008–1014

Balasubramanian A, Bhuva BL, Black JD, Massengill LW (2005) RHBD Techniques for Mitigating Effects of Single-Event Hits Using Guard-Gates. IEEE Trans Nucl Sci 52(6):2531–2535

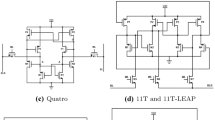

Li YQ, Wang HB, Liu R, Chen L, Nofal I, Shi ST, He AL, Guo G, Baeg SH, Wen SJ, Wong R, Chen M, Wu Q (2017) A Quatro-Based 65-nm Flip-Flop Circuit for Soft-Error Resilience. IEEE Trans Nucl Sci 64(6):1554–1561

Furuta J, Sonezaki E, Kobayashi K (2015) Radiation hardness evaluations of 65nm fully depleted silicon on insulator and bulk processes by measuring single event transient pulse widths and single event upset rates. Japanese J Appl Phys, 54(4S): 04DC15–1–04DC15–6.

Jagannathan S, Loveless TD, Diggins Z, Bhuva BL, Wen SJ, Wong R, Massengill LW (2011) Neutron-and alpha-particle induced soft-error rates for flip flops at a 40 nm technology node. In Proc IEEE Int Reliab Phys Symp (IPRS), SE.5.1-SE.5.5.

Ostler PS, Caffrey MP, Gibelyou DS, Graham PS, Morgan KS, Pratt BH, Quinn HM, Wirthlin MJ (2009) SRAM FPGA Reliability Analysis for Harsh Radiation Environments. IEEE Trans Nucl Sci 56(6):3519–3526

Liu R (2017) Study of Radiation Effects on 28nm UTBB FDSOI Technology. Doctoral Thesis, University of Saskatchewan.

Roche P, Gasiot G, Uznanski S, Daveau JM, Torras-Flaquer J, Clerc S, Harboe-Sørensen R (2009) A Commercial 65nm CMOS Technology for Space Applications: Heavy Ion, Proton and Gamma Test Results and Modeling. In Proceedings European Conference on Radiation and Its Effects on Components and Systems, pp: 456–464.

Asthana V, Kar M, Jimenez J, Haendler S, Galy P (2013) 6T SRAM performance and power gain using Double Gate MOS in 28nm FDSOI Technology. In Proceedings IEEE International Conference on IC Design & Technology (ICICDT), 89–92.

Balasubramanian P, Prasad K (2016) A Fault Tolerance Improved Majority Voter for TMR System Architectures. World Scientific and Engineering Academy and Society Transactions on Circuits and Systems 15:108–122

Guo G et al. (2011) Irradiation Facility and Technique to Increase LET for SEE testing on Tandem Accelerator. In Proceedings RADiation Effects on Components and Systems (RADECS), 724–728.

Zheng L-S, Ji D-M, Gong D, Shen C, Zhao J (2017) On the Low SEU Threshold-LET of 28nm FDSOI SRAM. In: Proceedings Modeling of Systems and Parameter Extraction Working Group. Available at: http://www.mos-ak.org/hangzhou_2017/publications/Shen_Chen_MOS-AK_Hanngzhou_2017.pdf

Roche P (2014) Latest 3D-TCAD Simulations and Radiation Test Results in UTBB FDSOI 28nm. In Proceedings 6th annual IEEE Santa Clara Valley SER Workshop. Available at: http://ewh.ieee.org/soc/cpmt/presentations/cpmt1410wb.pdf

Semiconductor Device Simulation, Cogenda, http://www.cogenda.com/

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: S. Hellebrand

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Shi, S., Chen, R., Liu, R. et al. Single Event Upset Evaluation for a 28-nm FDSOI SRAM Type Buffer in an ARM Processor. J Electron Test 37, 271–278 (2021). https://doi.org/10.1007/s10836-021-05940-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-021-05940-6