Abstract

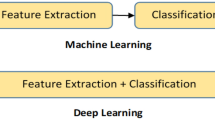

Wafer bin maps (WBM) provides crucial information regarding process abnormalities and facilitate the diagnosis of low-yield problems in semiconductor manufacturing. Most studies of WBM classification and analysis apply a statistical-based method or machine learning method operating on raw wafer data and extracted features. With increasing WBM pattern diversity and complexity, the useful features for effective WBM recognition are highly dependent on domain knowledge. This study proposes an ensemble convolutional neural network (ECNN) framework for WBM pattern classification, in which a weighted majority function is adopted to select higher weights for the base classifiers that have higher predictive performance. An industrial WBM dataset (namely, WM-811K) from a wafer fabrication process was used to demonstrate the effectiveness of the proposed ECNN framework. The proposed ECNN has superior performance in terms of precision, recall, F1 and other conventional machine learning classifiers such as linear regression, random forest, gradient boosting machine, and artificial neural network. The experimental results show that the proposed ECNN framework is able to identify common WBM defect patterns effectively.

Similar content being viewed by others

References

Badmos, O., Kopp, A., Bernthaler, T., & Schneider, G. (2020). Image-based defect detection in lithium-ion battery electrode using convolutional neural networks. Journal of Intelligent Manufacturing, 31(4), 885–897.

Baly, R., & Hajj, H. (2012). Wafer classification using support vector machines. IEEE Transactions on Semiconductor Manufacturing, 25(3), 373–383.

Chen, H., Pang, Y., Hu, Q., & Liu, K. (2020). Solar cell surface defect inspection based on multispectral convolutional neural network. Journal of Intelligent Manufacturing, 31(2), 453–468.

Chien, C. F., Hsu, C. Y., & Chang, K. H. (2013a). Overall wafer effectiveness (OWE): A novel industry standard for semiconductor ecosystem as a whole. Computers & Industrial Engineering, 65(1), 117–127.

Chien, C. F., Hsu, S. C., & Chen, Y. J. (2013b). A system for online detection and classification of wafer bin map defect patterns for manufacturing intelligence. International Journal of Production Research, 51(8), 2324–2338.

Duchi, J., Hazan, E., & Singer, Y. (2011). Adaptive subgradient methods for online learning and stochastic optimization. Journal of Machine Learning Research, 12, 2121–2159.

Fan, M., Wang, Q., & van der Waal, B. (2016). Wafer defect patterns recognition based on OPTICS and multi-label classification. In Proceedings of 2016 IEEE Advanced Information Management, Communicates, Electronic and Automation Control Conference (IMCEC) (pp. 912–915).

Galar, M., Fernandez, A., Barrenechea, E., Bustince, H., & Herrera, F. (2011). A review on ensembles for the class imbalance problem: Bagging-, boosting-, and hybrid-based approaches. IEEE Transactions on Systems, Man, and Cybernetics, Part C (Applications and Reviews), 42(4), 463–484.

Gonzalez-Val, C., Pallas, A., Panadeiro, V., & Rodriguez, A. (2020). A convolutional approach to quality monitoring for laser manufacturing. Journal of Intelligent Manufacturing, 31(3), 789–795.

Hsu, C. Y. (2014). Integrated data envelopment analysis and neural network model for forecasting performance of wafer fabrication operations. Journal of Intelligent Manufacturing, 25(5), 945–960.

Hsu, C. Y. (2015). Clustering ensemble for identifying defective wafer bin map in semiconductor manufacturing. Mathematical Problems in Engineering, Article no. 707358.

Hsu, C.-Y., Chen, W. J., & Chien, J. C. (2020). Similarity matching of wafer bin maps for manufacturing intelligence to empower industry 3.5 for semiconductor manufacturing. Computers & Industrial Engineering, 142, 106358.

Hsu, S. C., & Chien, C. F. (2007). Hybrid data mining approach for pattern extraction from wafer bin map to improve yield in semiconductor manufacturing. International Journal of Production Economics, 107(1), 88–103.

Hwang, J. Y., & Kuo, W. (2007). Model-based clustering for integrated circuit yield enhancement. European Journal of Operational Research, 178(1), 143–153.

Jeong, Y. S., Kim, S. J., & Jeong, M. K. (2008). Automatic identification of defect patterns in semiconductor wafer maps using spatial correlogram and dynamic time warping. IEEE Transactions on Semiconductor Manufacturing, 21(4), 625–637.

Jin, C. H., Kim, H.-J., Piao, Y., Li, M., & Piao, M. (2020). Wafer map defect pattern classification based on convolutional neural network features and error-correcting output codes. Journal of Intelligent Manufacturing, 1–15. https://doi.org/10.1007/s10845-020-01540-x.

Kingma, D. P., & Ba, J. (2014). Adam: A method for stochastic optimization. arXiv:1412.6980.

Krizhevsky, A., Sutskever, I., & Hinton, G. E. (2012). Imagenet classification with deep convolutional neural networks. In Proceedings of Advances in Neural Information Processing Systems (NIPS) Conference (pp. 1097–1105).

Kyeong, K., & Kim, H. (2018). Classification of mixed-type defect patterns in wafer bin maps using convolutional neural networks. IEEE Transactions on Semiconductor Manufacturing, 31(3), 395–402.

LeCun, Y., Bottou, L., Bengio, Y., & Haffner, P. (1998). Gradient-based learning applied to document recognition. Proceedings of the IEEE, 86(11), 2278–2324.

Lin, H., Li, B., Wang, X., Shu, Y., & Niu, S. (2019). Automated defect inspection of LED chip using deep convolutional neural network. Journal of Intelligent Manufacturing, 30(6), 2525–2534.

Liu, E., Chen, K., Xiang, Z., & Zhang, J. (2020). Conductive particle detection via deep learning for ACF bonding in TFT-LCD manufacturing. Journal of Intelligent Manufacturing, 31(4), 1037–1049.

Liu, C. W., & Chien, C. F. (2013). An intelligent system for wafer bin map defect diagnosis: An empirical study for semiconductor manufacturing. Engineering Applications of Artificial Intelligence, 26(5–6), 1479–1486.

Nakazawa, T., & Kulkarni, D. V. (2018). Wafer map defect pattern classification and image retrieval using convolutional neural network. IEEE Transactions on Semiconductor Manufacturing, 31(2), 309–314.

Nakazawa, T., & Kulkarni, D. V. (2019). Anomaly detection and segmentation for wafer defect patterns using deep convolutional encoder–decoder neural network architectures in semiconductor manufacturing. IEEE Transactions on Semiconductor Manufacturing, 32(2), 250–256.

Park, S., Jang, J., & Kim, C. O. (2020). Discriminative feature learning and cluster-based defect label reconstruction for reducing uncertainty in wafer bin map labels. Journal of Intelligent Manufacturing, 1–13. https://doi.org/10.1007/s10845-020-01571-4.

Piao, M., Jin, C. H., Lee, J. Y., & Byun, J. Y. (2018). Decision tree ensemble-based wafer map failure pattern recognition based on radon transform-based features. IEEE Transactions on Semiconductor Manufacturing, 31(2), 250–257.

Saha, S., & Ekbal, A. (2013). Combining multiple classifiers using vote based classifier ensemble technique for named entity recognition. Data & Knowledge Engineering, 85, 15–39.

Saqlain, M., Jargalsaikhan, B., & Lee, J. Y. (2019). A voting ensemble classifier for wafer map defect patterns identification in semiconductor manufacturing. IEEE Transactions on Semiconductor Manufacturing, 32(2), 171–182.

Shim, J., Kang, S., & Cho, S. (2020). Active learning of convolutional neural network for cost-effective wafer map pattern classification. IEEE Transactions on Semiconductor Manufacturing, 33(2), 258–266.

Szegedy, C., Liu, W., Jia, Y., Sermanet, P., Reed, S., Anguelov, D., Erhan, D., Vanhoucke, V., & Rabinovich, A. (2015), Going deeper with convolutions. In Proceedings of the IEEE conference on computer vision and pattern recognition (pp. 1–9).

Tieleman, T., & Hinton, G. (2012). Lecture 6.5-RMSProp, COURSERA: Neural networks for machine learning. Technical report.

Wang, R., & Chen, N. (2019). Wafer map defect pattern recognition using rotation-invariant features. IEEE Transactions on Semiconductor Manufacturing, 32(4), 596–604.

Wu, M. J., Jang, J. S. R., & Chen, J. L. (2015). Wafer map failure pattern recognition and similarity ranking for large-scale data sets. IEEE Transactions on Semiconductor Manufacturing, 28(1), 1–12.

Yu, J. (2019). Enhanced stacked denoising autoencoder-based feature learning for recognition of wafer map defects. IEEE Transactions on Semiconductor Manufacturing, 32(4), 613–624.

Yu, J., & Lu, X. (2016). Wafer map defect detection and recognition using joint local and nonlocal linear discriminant analysis. IEEE Transactions on Semiconductor Manufacturing, 29(1), 33–43.

Yu, N., Xu, Q., & Wang, H. (2019a). Wafer defect pattern recognition and analysis based on convolutional neural network. IEEE Transactions on Semiconductor Manufacturing, 32(4), 566–573.

Yu, J., Zheng, X., & Liu, J. (2019b). Stacked convolutional sparse denoising auto-encoder for identification of defect patterns in semiconductor wafer map. Computers in Industry, 109, 121–133.

Yuan, T., & Kuo, W. (2008a). A model-based clustering approach to the recognition of the spatial defect patterns produced during semiconductor fabrication. IIE Transactions, 40(2), 93–101.

Yuan, T., & Kuo, W. (2008b). Spatial defect pattern recognition on semiconductor wafers using model-based clustering and Bayesian inference. European Journal of Operational Research, 190(1), 228–240.

Yuan, T., Kuo, W., & Bae, S. J. (2011). Detection of spatial defect patterns generated in semiconductor fabrication processes. IEEE Transactions on Semiconductor Manufacturing, 24(3), 392–403.

Zeiler, M. D. (2012). Adadelta: An adaptive learning rate method. arXiv:1212.5701.

Acknowledgement

This research was supported by the Ministry of Science and Technology, Taiwan (MOST106-2628-E-027-002-MY3; MOST108-2813-C-027-017-E; MOST 108-2745-8-027-003).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Hsu, CY., Chien, JC. Ensemble convolutional neural networks with weighted majority for wafer bin map pattern classification. J Intell Manuf 33, 831–844 (2022). https://doi.org/10.1007/s10845-020-01687-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10845-020-01687-7