Abstract

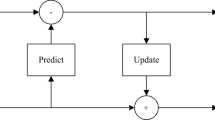

Image Compression is one of the emerging technique of Digital System for storing, retrieving of digital media applications. The main problem of Image Compression is requiring less space for storage and computation speed. In this paper we address this problem and develop a memory-efficient high speed architecture which is implemented based on orthonormalized multi-stage Fast-DST processing unit to perform lifting operation. The proposed multi-stage transform unit performs the split, predict and the update operations by considering the odd samples which are neglected in other lifting transforms. This results in speeding up the process because of the simultaneous execution of both samples. The RTU and CTU are erected with the aid of delay elements and the lifting coefficient, which further tends to attain the optimized processing speed. To address the problem of high cost of memory, multi stage proposed DST unit are combined to build a parallel multi-stage architecture which can perform multistage parallel execution on input image at competitive hardware cost. Finally, the proposed method attains better results when they are compared with existing in terms of memory complexity, low power, low latency.

Similar content being viewed by others

References

Aziz SM, Pham DM (2012) Efficient parallel architecture for multi-level forward discrete wavelet transform processors. Comput Electric Eng 38(5):1325–1335

Cheng C, Keshab Parhi K (2008) High-speed VLSI implementation of the 2-D discrete wavelet transform. IEEE Trans Signal Process 56(1):393–403

Darji A et al (2014) Dual-scan parallel flipping architecture for a lifting-based 2-D discrete wavelet transform. IEEE Trans Circ Syst II: Express Briefs 61(6):433–437

Das A, Hazra A, Banerjee S (2012) An efficient architecture for 3-D discrete wavelet transform. IEEE Trans Circ Syst Video Technol 20(2):286–296

Haghighi BB, Taherinia AH, Mohajerzadeh AH (2018) TRLG: Fragile blind quad watermarking for image tamper detection and recovery by providing compact digests with quality optimized using LWT and GA. arXiv preprint arXiv:1803.02623

Hashim AT, Ali SA Color image compression using DPCM with DCT, DWT and Quadtree Coding Scheme

Hsia C-H, Guo J-M, Chiang J-S (2009) Improved low-complexity algorithm for 2-D integer lifting-based discrete wavelet transforms using symmetric mask-based scheme. IEEE Trans Circ Syst Video Technol 19(8):1202–1208

Hsia C-H, Chiang J-S, Guo J-M (2013) Memory-efficient hardware architecture of 2-D dual-mode lifting-based discrete wavelet transform. IEEE Trans Circ Syst Video Technol 23(4):671–683

Huang H, Xiao L (2013) CORDIC based fast radix-2 DCT algorithm. IEEE Signal Process Lett 20(5):483–486

Huang C-T, Tseng P-C, Chen L-G (2015) Generic RAM-based architectures for two-dimensional discrete wavelet transform with the line-based method. IEEE Trans Circ Syst Video Technol 15(7):910–920

Imgraben S, Dittmann S Leaf litter dynamics and litter consumption in two temperate South Australian mangrove forests. J Sea Res 59(1–2):83–93

Kahu S, Rahate R (2013) Image compression using singular value decomposition. Int J Adv Res Technol 2(8):244–248

Krasikov A (2010) Socioeconomic determinants of infant mortality rate disparities. Clemson University

Lai Y-K, Chen L-F, Shih Y-C (2009) A high-performance and memory-efficient VLSI architecture with parallel scanning method for 2-D lifting-based discrete wavelet transform. IEEE Trans Consum Electron 55(2):400–407

Lai Y-K, Chen L-F, Shih Y-C A high-performance and memory-efficient VLSI architecture with parallel scanning method for 2-D lifting-based discrete wavelet transform. IEEE Trans Consumer Electron 55(2):400–407

Lee S-J et al (2010) 3-D system-on-system (SoS) biomedical-imaging architecture for health-care applications. IEEE Trans Biomed Circ Syst 4(6):426–436

Liang D et al (2013) Stacked phased array coils for increasing the signal-to-noise ratio in magnetic resonance imaging. IEEE Trans Biomed Circ Syst 7(1):24–30

Mohanty Basant K, Pramod Meher K (2011) A memory-efficient architecture for 3-D DWT using an overlapped grouping of frames. IEEE Trans Signal Process 59(11):5605–5616

Mohanty Basant K, Mahajan A, Pramod Meher K (2012) Area-and power-efficient architecture for high-throughput implementation of lifting 2-D DWT. IEEE Trans Circ Syst II: Express Briefs 59(7):434–438

Mohanty BK, Meher PK (2013) Memory-efficient high-speed convolution-based generic structure for multilevel 2-D DWT. IEEE Trans Circ Syst Video Technol 23(2):353–363

Nian YJ et al. (2012) Near-lossless compression of hyperspectral images based on distributed source coding. Science China Inf Sci: 1–10

Oweiss KG et al (2007) A scalable wavelet transform VLSI architecture for real-time signal processing in high-density intra-cortical implants. IEEE Trans Circ Syst I: Reg Papers 54(6):1266–1278

Seo Y-H, Kim D-W (2010) A new VLSI architecture of parallel multiplier–accumulator based on Radix-2 modified booth algorithm. IEEE Trans Very Large Scale Integ (VLSI) Syst 18(2):201–208

Tian X et al (2011) Efficient multi-input/multi-output VLSI architecture for two-dimensional lifting-based discrete wavelet transform. IEEE Trans Comput 60(8):1207–1211

Wu B-F, Lin C-F (2005) A high-performance and memory-efficient pipeline architecture for the 5/3 and 9/7 discrete wavelet transform of JPEG2000 codec. IEEE Trans Circ Syst Video Technol 15(12):1615–1628

Wu BF, Lin CF A high-performance and memory-efficient pipeline architecture for the 5/3 and 9/7 discrete wavelet transform of JPEG2000 codec. IEEE Trans Circ Syst Video Technol 15(12):1615–1628

Xiong C-Y, Tian J-W, Liu J (2006) A note on flipping structure: an efficient VLSI architecture for lifting-based discrete wavelet transform. IEEE Trans Signal Process 54(5):1910–1916

Xiong C, Tian J, Liu J (2007) Efficient architectures for two-dimensional discrete wavelet transform using lifting scheme. IEEE Trans Image Process 16(3):607–614

Xiong C, Tian J, Liu J Efficient architectures for two-dimensional discrete wavelet transform using lifting scheme. IEEE Trans Image Process 16(3):607–614

Zhang W et al (2012) An efficient VLSI architecture for lifting-based discrete wavelet transform. IEEE Trans Circ Syst II: Express Briefs 59(3):158–162

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

kiranmaye, G., Tadisetty, S. A novel ortho normalized multi-stage discrete fast Stockwell transform based memory-aware high-speed VLSI implementation for image compression. Multimed Tools Appl 78, 17673–17699 (2019). https://doi.org/10.1007/s11042-018-7055-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11042-018-7055-5