Abstract

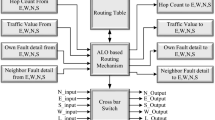

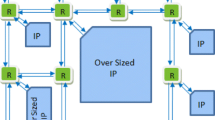

A power and latency efficient scheme for on-chip network communication is presented and its performance is analyzed. This new scheme is designed for a general architecture with a buffered/bufferless router (BR/BLR), which eliminates buffers in the majority of routers to achieve power efficiency while keeping buffers in a few routers to facilitate various desirable services and to reduce latency. Extensive simulation shows that the proposed scheme performs better than purely bufferless as well as buffered approach under different synthetic traffic patterns.

Similar content being viewed by others

References

Dally WJ, Towles B (2001) Route packets, not wires: on-chip interconnection networks. In: Proceeding of design automation conference, pp 684–689

Benini L, Micheli GD (2002) Networks on chips: a new SoC paradigm. Computer 35:70–78

Marculescu R, Ogras UY, Peh L-S, Jerger NE, Hoskote Y (2009) Outstanding research problems in NoC design system microarchitecture and circuit perspectives. IEEE Trans Comput-Aided Des Integr Circuits Syst 28:3–21

Meincke T et al (1999) Globally asynchronous locally synchronous architecture for large high-performance ASICs. In: Proceeding of international symposium on circuits and systems, vol 2, pp 512–515

Shang L, Peh L-S, Jha NK (2003) Dynamic voltage scaling with links for power optimization of interconnection networks. In: Proceeding of international symposium on high performance computer architecture, pp 91–102

Balfour J, Dally WJ (2006) Design tradeoffs for tiled CMP on-chip networks. In: Proceeding of international conference on supercomputing, pp 187–198

Kodi AK, Sarathy A, Louri A (2008) iDEAL: inter-router dual-function energy and area-efficient links for network-on-chip (NoC) architecture. In: Proceeding of international symposium on computer architecture, pp 241–250

Kim J (2009) Low-cost router microarchitecture for on-chip networks. In: Proceeding of IEEE/ACM international symposium on microarchitecture, pp 255–266

Moscibroda T, Mutlu O (2009) A case for bufferless routing in on-chip networks. In: Proceeding of international symposium on computer architecture, pp 196–207

Vangal SR et al (2008) An 80-tile sub-100-W TeraFLOPS processor in 65-nm CMOS. IEEE J Solid-State Circuits 43:29–41

Gomez C, Gomez ME, Lopez P, Duato J (2008) Reducing packet dropping in a bufferless NoC. In: Proceeding of international Euro-Par conference on parallel processing, pp 899–909

Hayenga M, Jerger NE, Lipasti M (2009) SCARAB: a single cycle adaptive routing and bufferless network. In: MICRO’09, pp 244–254

Bouhraoua A, Elrabaa MES (2007) An efficient network-on-chip architecture based on the fat-tree (FT) topology. Arab J Sci Eng 32:13–26

Gratz P, Kim C, McDonald R, Keckler SW, Burger D (2006) Implementation and evaluation of on-chip network architectures. In: Proceeding of international conference on computer design, pp 477–484

Hu J, Marculescu R (2004) Application-specific buffer space allocation for networks-on-chip router design. In: IEEE/ACM international conference on computer-aided design, pp 354–361

Michelogiannakis G, Sanchez D, Dally WJ, Kozyrakis C (2010) Evaluating bufferless flow control for on-chip networks. In: Proceeding of IEEE/ACM international symposium on networks-on-chip, pp 9–16

Ni LM, Mckinley PK (1993) A survey of wormhole routing techniques in direct networks. Computer 26:62–76

Lu Z (2005) Using wormhole switching for networks on chip: feasibility analysis and micro-architecture adaptation. Licentiate thesis, Royal Institute of Technology

Lu Z, Zhong M, Jantsch A (2006) Evaluation of on-chip networks using deflection routing. In: Proceeding of ACM Great Lakes symposium on VLSI, pp 296–301

Dally WJ, Towles BP (2004) Principles and practices of interconnection networks. Morgan Kaufmann, San Mateo

Ogras UY, Marculescu R, Lee HG, Chang N (2006) Communication architecture optimization: making the shortest path shorter in regular networks-on-chip. In: Proceeding of the design automation and test in Europe, pp 712–717

http://nocs.stanford.edu/cgi-bin/trac.cgi/wiki/Resources/BookSim

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Lin, J., Lin, X. Power and latency efficient mechanism: a seamless bridge between buffered and bufferless routing in on-chip network. J Supercomput 61, 1048–1067 (2012). https://doi.org/10.1007/s11227-011-0676-3

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-011-0676-3