Abstract

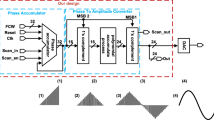

In this work, a new direct digital frequency synthesizer (DDFS) is proposed, which is based on a new two-level table-lookup (TLTL) scheme combined with Taylor’s expansion. This method only needs a lookup-table size of total \(n \times 2^{{n \mathord{\left/ {\vphantom {n {4 + 1}}} \right. \kern-\nulldelimiterspace} {4 + 1}}} + {\left( {n \mathord{\left/ {\vphantom {n {4 - 2}}} \right. \kern-\nulldelimiterspace} {4 - 2}} \right)} \times 2^{{n \mathord{\left/ {\vphantom {n 4}} \right. \kern-\nulldelimiterspace} 4}}\) bits, one \({\left( {n + 1} \right)} \times {3n} \mathord{\left/ {\vphantom {{3n} 4}} \right. \kern-\nulldelimiterspace} 4 - {\text{bit}}\) multiplier, one n × 3n/4-bit multiplier and two additional smaller multipliers, to generate both sine and cosine values (where n is the output precision). Compared with several notable DDFS’s, the new design has a smaller lookup-table size and higher SFDR (Spurious Free Dynamic Range) for high-precision output cases, at comparable multiplier and adder complexities. The DDFS is verified by FPGA and EDA tools using Synopsys Design Analyzer and UMC 0.25 μm cell library, assuming 16-bit output precision. The designed 16-bit DDFS has a small gate count of 2,797, and a high SFDR of 110 dBc.

Similar content being viewed by others

References

D. A. Sunderland, R. A. Strauch, S. S. Wharfield, H. T. Peterson and C. R. Cole, “CMOS/SOS Frequency Synthesizer LSI Circuit for Spread Spectrum Communications,” IEEE J. Solid-State Circuits, vol. 19, 1984, pp. 497–505, Aug.

A. Bellaouar, M. S. O’brecht, A. M. Fahim and M. I. Elmasry, “Low-Power Direct Digital Frequency Synthesis for Wireless Communications,” IEEE J. Solid-State Circuits, vol. 35, 2000, pp. 385–390.

S. Mortezapour and E. K. F. Lee, “Design of Low-Power ROM-Less Direct Digital Frequency Synthesizer Using Nonlinear Digital-to-Analog Converter,” IEEE J. Solid-State Circuits, vol. 34, 1999, pp. 1350–1359.

L. Lo Presti and G. Cardamone, “A Direct Digital Frequency Synthesizer Using an IIR Filter Implemented with a DSP Microprocessor,” Proceedings of IEEE International Conference on Acoustics, Speech, and Signal Processing, vol. 3, 1994, pp. 201–204.

M. M. Al-Ibrahim, “A Simple Recursive Digital Sinusoidal Oscillator with Uniform Frequency Spacing,” Proceedings of IEEE International Symposium on Circuits Systems, vol. 2, 2001, pp. 689–692.

D. Das Sarma and D. W. Matula, “Faithful Bipartite ROM Reciprocal Tables,” Proceedings of 12th Symposium on Computer Arithmetic, 1995, pp. 17–29.

F. Curticapean and J. Niittylahti, “A Hardware Efficient Direct Digital Frequency Synthesizer,” Proceedings of IEEE International Conference on Electronics, Circuits and Systems, vol. 1, 2001, pp. 51–54.

F. Curticapean and J. Niittylahti, “Low-Power Direct Digital Frequency Synthesizer,” Proceedings of IEEE International Symposium on Circuits Systems, 2000, pp. 822–825.

J. M. P. Langlois and D. Al-Khalili, “Novel Approach to the Design of Direct Digital Frequency Synthesizers Based on Linear Interpolation,” IEEE Transactions on Circuits System II: Analog and Digital Signal Processing, vol. 50, no. 9, 2003, pp. 567–578.

Y. K. Chang and E. E. Swartzlander, “An Analysis of the CORDIC Algorithm for Direct Digital Frequency Synthesis,” Proceedings of Application-Specific Systems, Architectures and Processor, 2002, pp. 111–119.

A. Madisetti, A. Y. Kwentus and A. N. Wilson, “A 100-MHz, 16-b, Direct Digital Frequency Synthesizer with a 100-dBc Spurious-Free Dynamic Range,” IEEE J. Solid-State Circuits, vol. 34, no. 8, 1999, pp. 1034–1043.

J. C. Chih, J. Y. Chou and S. G. Chen, “An Efficient Direct Digital Frequency Synthesizer Based on Two-level Table-Lookup,” Proceedings of Frequency Control System and PDA Exhibition, 2001, pp. 824–827.

C. C. Wang, H. C. She and H. Ron, “A ROM-Less Direct Digital Frequency Synthesizer by Using Trigonometric Quadruple Angle Formula,” Proceedings of IEEE International Conference on Electronics, Circuits, and Systems, vol. 1, 2002, pp. 65–68.

D. De Caro, E. Napoli and A. G. M. Strollo, “Direct Digital Frequency Synthesizers with Polynomial Hyperfolding Technique,” IEEE Trans. Circuits Syst., vol. 51, 2004, pp. 337–344.

A. M. Sodagar and G. Roientan, “A Novel Architecture for ROM-less Sine-Output Direct Digital, Frequency Synthesizers by Using the 2-Order Parabolic Approximation,” Proceedings of Frequency Control System and PDA Exhibition, 2000, pp. 284–289.

K. I. Palomaki and J. Niittylahti, “Direct Digital Frequency Synthesizer Architecture Based on Chebyshev Approximation,” Proceedings of Signals, Systems and Computers, vol. 2, 2000, pp. 1639–1643.

L. Fanucci, R. Roncella and R. Saletti, “A Sine Wave Digital Synthesizer Based on A Quadratic Approximation,” Proceedings of Frequency Control System and PDA Exhibition, 2001, pp, 806–810.

A. M. Sodagar and G. R. Lahiji, “Mapping From Phase to Sine-Amplitude in Direct Digital Frequency Synthesizers Using Parabolic Approximation,” IEEE Trans. Circuits Syst., vol. 47, 2000, pp. 1452–1457, Dec.

S. Yonachul and K. Beomsup, “A 16b Quadrature Direct Digital Frequency Synthesizer Using Interpolative Angle Rotation Algorithm,” VLSI Circuits Digest of Technical Papers, 2002, pp. 146–147.

M.-S. Lin, C.-S. Yang, C.-Y. Chu and S.-G. Chen, “An Efficient Pipeline Direct Digital Frequency Synthesizer Based on a Novel Interpolation Algorithm,” Proceedings of the 2001 European Conference on Circuit Theory and Design, 2001, pp. 273–276.

A. A. Karatsuba and Y. P. Ofman, “Multiplication of Multidigit Numbers on Automata,” Sov. Phys. Dokl., vol. 7, 1963, pp. 595–596.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Chen, SG., Chih, JC. & Chou, JY. Direct Digital Frequency Synthesis Based on a Two-Level Table-Lookup Scheme. J VLSI Sign Process Syst Sign Image Video Technol 45, 153–160 (2006). https://doi.org/10.1007/s11265-006-9763-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-006-9763-8