Abstract

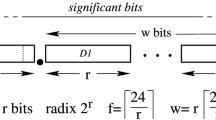

Range reduction is a crucial step for the accuracy in trigonometric functions evaluation. A new pipelined architecture to deal with range reduction for floating point representation is presented in this paper. The algorithm is based on a look-up table storing the corresponding powers of 2 mod A. The overall design has been optimized for a modulo equal to 2π, which is the most widely used due to trigonometric functions requirements. We provide an evaluation of different configurations and a full error propagation study which ensures an accuracy of one unit in the last place.

Similar content being viewed by others

References

Muller, J. M. (1997). Elementary functions, algorithms and implementation. Boston: Birkhauser.

Brisebarre, N., Defour, D., Kornerup, P., Muller, J. M., & Revol, N. (2005). A new range-reduction algorithm. IEEE Transactions on Computers, 54, 331–339 (March).

Cody, W., & Waite, W. (1980). Software manual for the elementary functions. Englewood Cliffs, NJ: Prentice-Hall.

Daumas, M., Mazenc, C., Merrheim, X., & Muller, J. M. (1995). Modular range reduction: a new algorithm for fast and accurate computation of the elementary functions. Universal Journal of Computer Science, 1, 162–175 (March).

Payne, M., & Hanek, R. (1983). Radian reduction for trigonometric functions. SIGNUM Newsletter, 18, 19–24.

Villalba, J., Lang, T., & González, M. A. (2006). Double-residue modular range reduction for floating-point hardware implementations. IEEE Transactions on Computers, 55, 254–267 (March).

Koc, C. K., & Hung, C. Y. (1998). Fast algorithm for modular reduction. In IEEPCDT: IEE proceedings on computers and digital techniques (Vol. 145). Piscataway: IEEE.

Ercegovac, M. D., & Lang, T. (2004). Digital arithmetic. San Francisco, CA: Morgan Kaufmann.

Kahan, W. (1996). Lecture notes on the status of IEEE 754. http://http.cs.berkeley.edu/~wkahan/ieee754status/ieee754.ps.

Smith, R. A. (1995). A continued-fraction analysis of trigonometric argument reduction. IEEE Transactions on Computers, 44(11), 1348–1351 (November).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Jaime, F.J., Villalba, J., Hormigo, J. et al. Pipelined Architecture for Additive Range Reduction. J Sign Process Syst Sign Image Video Technol 53, 103–112 (2008). https://doi.org/10.1007/s11265-008-0166-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-008-0166-x