Abstract

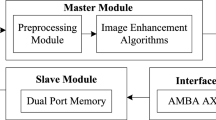

MPSoC (Multi-Processor System-on-Chip) architecture is becoming increasingly used because it can provide designers much more opportunities to meet specific performance and power goals. In this paper, we propose an MPSoC architecture for implementing real-time signal processing in gamma camera. Based on a fully analysis of the characteristics of the application, we design several algorithms to optimize the systems in terms of processing speed, power consumption, and area costs etc. Two types of DSP core have been designed for the integral algorithm and the coordinate algorithm, the key parts of signal processing in a gamma camera. An interconnection synthesis algorithm is proposed to reduce the area cost of the Network-on-Chip. We implement our MPSoC architecture on FPGA, and synthesize DSP cores and Network-on-Chip using Synopsys Design Compiler with a UMC 0.18 \(\upmu\textrm m\) standard cell library. The results show that our technique can effectively accelerate the processing and satisfy the requirements of real-time signal processing for 256 × 256 image construction.

Similar content being viewed by others

References

IBM On-chip CoreConnect bus architecture. www.chips.ibm.com .

ARM 920T, Rev. 1, Technical reference manual (2001).

ARM AMBA Specification (rev2.0) (2001). www.arm.com.

WISHBONE Interconnect Matrix IP Core. Rev. 1.1 (2002). www.opencores.org.

WISHBONE System-on-Chip (SoC) Interconnection Architecture for Portable IP Cores Revision: B.3 (2002). www.opencores.org.

STBus Communication System: Concepts and Definitions, Reference Guide. STMicroelectronics (2003).

Benini, L. (2006). Application specific noc design. In DATE ’06: Proceedings of the conference on design, automation and test in Europe (pp. 491–495). 3001 Leuven, Belgium, Belgium: European Design and Automation Association.

Benini, L., & Micheli, G. D. (2002). Networks on chips: A new soc paradigm. Computer, 35(1), 70–78.

Beric, A., Sethuraman, R., Pinto, C. A., Peters, H., Veldman, G., van de Haar, P., et al. (2006). Heterogeneous multiprocessor for high definition video. In Consumer electronics, 2006. ICCE ’06. 2006 Digest of technical papers. International Conference on (pp. 401–402).

Bertozzi, D., Jalabert, A., Murali, S., Tamhankar, R., Stergiou, S., Benini, L., et al. (2005). Noc synthesis flow for customized domain specific multiprocessor systems-on-chip. IEEE Transactions on Parallel and Distributed Systems, 16(2), 113–129.

Bjerregaard, T., & Mahadevan, S. (2006). A survey of research and practices of network-on-chip. ACM Computing Surveys, 38(1), 1.

Burger, D., & Austin, T. M. (1997). The simplescalar tool set, version 2.0. SIGARCH Computer Architecture News, 25(3), 13–25.

Garey, M. R., & Johnson, D. S. (1979). Computers and intractability: A guide to the theory of NP-completeness. New York: Freeman.

Jeong, M. H., Choi, Y., Chung, Y. H., Song, T. Y., Jung, J. H., Hong, K. J., et al. (2004). Performance improvement of small gamma camera using nai(tl) plate and position sensitive photo-multiplier tubes. Physics in Medicine and Biology, 49(21), 4961–4970.

Khatib, I. A., Poletti, F., Bertozzi, D., Benini, L., Bechara, M., Khalifeh, H., et al. (2006). A multiprocessor system-on-chip for real-time biomedical monitoring and analysis: architectural design space exploration. In E. Sentovich (Ed.), DAC (pp. 125–130). New York: ACM.

Kim, M., Banerjee, S., Dutt, N., & Venkatasubramanian, N. (2006). Design space exploration of real-time multi-media mpsocs with heterogeneous scheduling policies. In CODES+ISSS ’06: Proceedings of the 4th international conference on Hardware/software codesign and system synthesis (pp. 16–21). New York, NY, USA: ACM.

Kumar, R., Tullsen, D. M., Jouppi, N. P., & Ranganathan, P. (2005). Heterogeneous chip multiprocessors. Computer, 38(11), 32–38.

Manolache, S., Eles, P., Peng, Z. (2006). Buffer space optimisation with communication synthesis and traffic shaping for nocs. In DATE ’06: Proceedings of the conference on design, automation and test in Europe (pp. 718–723). 3001 Leuven, Belgium, Belgium: European Design and Automation Association.

Paker, O., Sparso, J., Haandbak, N., Isager, M., & Nielsen, L. S. (2004). A low-power heterogeneous multiprocessor architecture for audio signal processing. VLSI, Journal of Signal Processing, 37(1), 95–110.

Park, J., Song, H., Cho, S., Han, N., Kim, K., & Park, J. (2006). A real-time media framework for asymmetric mpsoc. In ISORC ’06: Proceedings of the Ninth IEEE international symposium on object and component-oriented real-time distributed computing (ISORC’06) (pp. 205–207). Washington, DC, USA: IEEE Computer Society.

Pasricha, S., & Dutt, N. (2006). Cosmeca: application specific co-synthesis of memory and communication architectures for mpsoc. In DATE ’06: Proceedings of the conference on design, automation and test in Europe (pp. 700–705). 3001 Leuven, Belgium, Belgium: European Design and Automation Association.

Pasricha, S., Dutt, N. D., & Ben-Romdhane, M. (2006). Constraint-driven bus matrix synthesis for mpsoc. In ASP-DAC (pp. 30–35).

Paul, J. M., Thomas, D. E., & Cassidy, A. S. (2005). High-level modeling and simulation of single-chip programmable heterogeneous multiprocessors. ACM Transactions on Design Automation of Electronic Systems, 10(3), 431–461.

Paulin, P. G., Pilkington, C., Bensoudane, E., Langevin, M., & Lyonnard, D. (2004). Application of a multi-processor soc platform to high-speed packet forwarding. In DATE ’04: Proceedings of the conference on design, automation and test in Europe (pp. 30058). Washington, DC, USA: IEEE Computer Society.

Reyes, V., Kruijtzer, W., Bautista, T., Alkadi, G., & Nnuez, A. (2006). A unified system-level modeling and simulation environment for mpsoc design: Mpeg-4 decoder case study. In DATE ’06: Proceedings of the conference on design, automation and test in Europe (pp. 474–479). 3001 Leuven, Belgium, Belgium: European Design and Automation Association.

Sanchez, F., Benlloch, J. M., Escat, B., Pavon, N., Porras, E., Kadi-Hanifi, D., et al. (2004). Design and tests of a portable mini gamma camera. Medical Physics, 31, 1384–1397.

Sanchez, F., Fernandez, M. M., Gimenez, M., Rodriguez-Alvarez, J. M. B. J. M. M. J., Quiros, F. G. D., Lerche, C. W., D., et al. (2006). Performance tests of two portable mini gamma cameras for medical applications. Medical Physics, 33, 4210–4220.

Shee, S. L., Erdos, A., & Parameswaran, S. (2006). Heterogeneous multiprocessor implementations for jpeg: A case study. In CODES+ISSS ’06: Proceedings of the 4th international conference on hardware/software codesign and system synthesis (pp. 217–222). New York, NY, USA: ACM.

Acknowledgements

The work described in this paper is partially supported by the grants from the Research Grants Council of the Hong Kong Special Administrative Region, China (CERG 526007 (PolyU B-Q06B) and PolyU A-PH41), the National Nature Science Foundation of China (60525314), the 973 Program of China (2002CB312204-04) and the 863 Program of China (2006AA04Z206).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Sun, K., Wang, M., Shao, Z. et al. Design and Synthesis of a Multiprocessor System-on-Chip Architecture for Real-Time Biomedical Signal Processing in Gamma Cameras. J Sign Process Syst Sign Image Video Technol 59, 71–83 (2010). https://doi.org/10.1007/s11265-008-0278-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-008-0278-3