Abstract

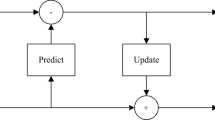

In this paper, we propose an efficient pipeline architecture for the DWT 9/7 filter defined in JPEG 2000. The proposed architecture is composed of column and row processors to perform the separable 2-D DWT. Based on the rescheduling DWT algorithm, we derive a new data flow graph to shorten the critical path. The proposed 1-D column processor requires less pipeline registers to achieve about the same critical path compared with other lifting-based architectures. For the row processor, the data dependency of each lifting step is reduced to only two computation nodes and therefore more pipeline registers can be applied to achieve higher processing speed without increasing the internal memory size in the 2-D case. That is, for an N × N image, it only requires 4N internal memory to perform the row-wise transform. For the memory bit-width analysis, we use software simulation to reduce the memory bit-width for various compression ratios. Since a portion of information from least significant bits of DWT coefficients would be discarded after EBCOT-tier2 processing, one can decrease the data width of internal memory to perform various compression ratios of JPEG 2000 coding, especially at the low-bit rates. Our simulation results suggest that it is practically possible to design the energy-aware memory architecture to further reduce the power consumption in the future work.

Similar content being viewed by others

References

ISO/IEC. ISO/IEC 15444-1. Information technology–JPEG 2000 image coding system, 2000.

Daubechies, I., & Sweldens, W. (1998). Factoring wavelet transform into lifting steps. The J of Fourier Analysis and Applications, 4, 247–269.

Jou, J. M., Shiau, Y. H., & Liu, C. C. (2001). Efficient VLSI architectures for the biorthogonal wavelet transform by filter bank and lifting scheme. in Proc. IEEE International Symposium on Circuits and Systems, 2, 529–532.

Wu, B. F., & Lin, C. F. (2003). A rescheduling and fast pipeline VLSI architecture for lifting-based discrete wavelet transforms. in Proc. IEEE International Symposium on Circuits and Systems, 2, 732–735.

Huang, C. T., Tseng, P. C., & Chen, L. G. (2004). Flipping structure: an efficient VLSI architecture for lifting-based discrete wavelet transform. IEEE Transactions on Signal Processing, 52(4), 1080–1089.

Liao, H., Mandal, M. K., & Cockburn, B. F. (2004). Efficient architectures for 1-D and 2-D lifting-based wavelet transforms. IEEE Transactions on Signal Processing, 52(5), 1315–1326.

Wu, B. F., & Lin, C. F. (2005). A high-performance and memory-efficient pipeline architecture for the 5/3 and 9/7 Discrete wavelet Transform of JPEG2000 codec. IEEE Transactions on Circuits and Systems for Video Technology, 15, 1615–1628.

Chang, T. H., Lian, C. J., Chen, H. H., Chang, J. Y., & Chen, L. G. (2003). Effective hardware-oriented technique for the rate control of JPEG2000 encoding. in Proc IEEE International Symposium on Circuits and Systems, 2, 684–687.

W. Yu (2004). Integrated rate control and entropy coding for JPEG 2000. in Proc. IEEE Data Compression Conference, 152–161.

Huang, C. T., Tseng, P. C., & Chen, L. G. (2004). Memory analysis and architecture for two-dimensional discrete wavelet transform. in Proc. IEEE International Conference on Acoustics, Speech, and Signal Processing, 5, 13–16.

Huang, C. T., Tseng, P. C., & Chen, L. G. (2005). Generic RAM-based architectures for two-dimensional discrete wavelet transform with line-based method. IEEE Transactions on Circuits and Systems for Video Technology, 15(7), 910–920.

Rabaey J. M., & Pedram, M. (2002). Power Aware Design Methodologies: Power Optimization by Datapath Width Adjustment (Chapter 7). Kluwer Academic Publishers.

JPEG 2000 Software model [Online]. Available: http://www.ece.uvic.ca/~mdadams/jasper/

Bhardwaj, M., Min, R., & Chandrakasan, A. P. (2001). Quantifying and enhancing power awareness of VLSI systems. IEEE Transactions on VLSI Systems, 9(6), 757–772.

Author information

Authors and Affiliations

Corresponding author

Additional information

This research was supported by National Science Council under Grant no. NSC 97-2221-E-009-072.

Rights and permissions

About this article

Cite this article

Lin, CF., Huang, PK. & Wu, BF. An Efficient Pipeline Architecture and Memory Bit-Width Analysis for Discrete Wavelet Transform of the 9/7 Filter for JPEG 2000. J Sign Process Syst Sign Image Video Technol 59, 245–253 (2010). https://doi.org/10.1007/s11265-009-0375-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-009-0375-y