Abstract

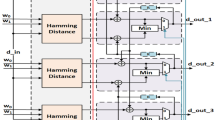

Viterbi decoder is a common module in communication system, which has the requirement of low power and low decoding latency. The conventional register exchange (RE) algorithm and memory-based trace-back (TB) algorithm cannot meet both constraints of power and decoding latency. In this paper, we propose a new Survivor Memory Unit (SMU) algorithm, named State Exchange (SE) algorithm. The SE algorithm uses the trace-forward unit (TFU) to run the decoding operation for low decoding latency. Besides, we enhance the SE algorithm by the concept of the trace-back (TB). Based on this enhancement, we propose two types of SE-SMU. Proposed type-I SE-SMU has lower register requirement with a long critical path. Proposed type-II SE-SMU can support the high speed requirement with the cost of additional TFUs and latency. Both two proposed SE-SMUs have the decoding latency slightly higher than the decoding latency of RE-SMU. We synthesized the proposed architecture in TSMC 0.13 um technology. Both two approaches have fewer active registers as decoding. From the power analysis, proposed SE-SMUs can give a 70% power reduction comparing with RE-SMU at 100 MHz with the decoding length = 96. The power saving ration will increase further with the longer decoding length.

Similar content being viewed by others

References

Viterbi, A. J. (1971). Convolutional codes and their performance in communication systems. IEEE Transactions on Communications, COM-19, no. 10, 751–771.

IEEE Std. 802.11 (1999). Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) specifications: High speed physical layer in the 5 GHz band.

Zweigle, G., Berge, T.J., Winterrowd, P., Makhani, A. (1995). A Viterbi, convolutional interleave, and Reed-Solomon decoder IC. In Proc. IEEE international conference on consumer electronics (pp. 34–35).

Hosemann, M., Habendorf, R., Fettweis, G.P. (2003). Hardware-software codesign of a 14.4 MBit—64 state—Viterbi decoder for an application-specific digital signal processor. In: Proc. IEEE Workshop on Signal Processing Systems (SiPS-2003) (pp. 27–29).

Steinert, M. & Marsili, S. (2004). Power consumption optimization for low latency Viterbi Decoder. In: Proc. IEEE Int. Symp. Circuits and Systems (ISCAS-2004), vol. II (pp. 377–380).

Chan, F., & Haccoun, D. (1997). Adaptive Viterbi decoding of convolutional codes over memoryless channels. IEEE Transactions on Communications, 45(11), 1389–1400.

Henning, R., & Chakrabarti, C. (2004). An approach for adaptively approximating the Viterbi algorithm to reduce power consumption while decoding convolutional codes. IEEE Transaction on Signal Processing, 52(5), 1443–1451.

Sun, F., & Zhang, T. (2007). Low-power state-parallel relaxed adaptive Viterbi decoder. IEEE Transaction on Circuits System, I: Regional Papers, 54(5), 1060–1068.

El-Dib, D. A., & Elmasry, M. I. (2004). Modified register-exchange Viterbi decoder for low-power wireless communications. IEEE Transaction on Circuits System, I: Regional Papers, 51(2), 371–378.

Shieh, M. D., Wang, T. P., & Yang, D. W. (2009). Low-power register-exchange survivor memory architectures for Viterbi decoders. IET Circuits Devices and Systems, 3, iss. 2, 83–90.

Chu, C. Y., Huang, Y. C.,& Wu, A. Y. (2008). Power efficient low latency survivor memory architecture for Viterbi decoder. In: Proc. IEEE Int. Symp. VLSI Design, Automation and Test (VLSI-DAT 2008) (pp. 228–231).

Tang, Y. C., Hu, D. C., Wei, W. Y., Lin, W. C., & Lin, H. C. (2009). A memory-efficient architecture for low latency Viterbi decoders. In: Proc. IEEE Int. Symp. VLSI Design, Automation and Test (VLSI-DAT 2009) (pp. 335–338).

Gang, Y., Erdogan, A. T., & Arslan, T. (2006). An efficient pre-traceback architecture for the Viterbi decoder targeting wireless communication applications. IEEE Transaction on Circuits System I: Regional Papers, 53(9), 1918–1927.

Kamuf, M., Owall, V., & Anderson, J. B. (2007). Survivor path processing in Viterbi decoders using register exchange and traceforward. IEEE Transaction on Circuits System II: Express Briefs, 54(6), 537–541.

Kamuf, M., Owall, V., & Anderson, J. B. (2008). Optimization and implementation of a Viterbi decoder under flexibility constraints. IEEE Transaction on Circuits System I: Regional Papers, 55(8), 2411–2422.

Hallin, J., Kjellberg, T., & Swahn, T. (2006). A 165-Gb/s 4:1 multiplexer in InP DHBT technology. IEEE Journal of Solid State Circuits, 41(10), 2209–2214.

Chien, J. C., & Lu, L. H. (2006). A 15-Gb/s 2:1 multiplexer in 0.18-μm CMOS. IEEE Microwave and Wireless Components Letters, 16(10), 558–560.

Author information

Authors and Affiliations

Corresponding author

Additional information

Financial supports from the SoC Technology Center (STC) at Industrial Technology Research Institute (ITRI) and NSC (grant no. NSC 96–2219- E-002-020) are greatly appreciated. The material in this paper was presented in part at the VLSI-DAT, Hsinchu, R.O.C., April 2008.

Rights and permissions

About this article

Cite this article

Chu, CY., Wu, AY. Power-Efficient State Exchange Scheme for Low-Latency SMU Design of Viterbi Decoder. J Sign Process Syst 68, 233–245 (2012). https://doi.org/10.1007/s11265-011-0603-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-011-0603-0