Abstract

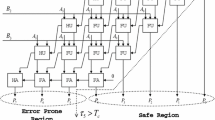

Aggressive power supply voltage V d d scaling is widely utilized to exploit the design margin introduced by the process, voltage and environment variations. However, scaling beyond the critical V d d results to numerous setup timing errors, and hence to an unacceptable output quality. In this paper, we propose computation-skip (CS) scheme to mitigate setup timing errors, for recursive digital signal processors with a fixed cycles per instruction (CPI). A coordinate rotation digital computer (CORDIC) with the proposed CS scheme still functions when scaling beyond the error-free voltage. It enables better-than-worst-case design constraint and achieves 1.82 X energy saving w.r.t. nominal V d d condition, another 1.49 X energy saving without quality degradation, and another 1.09 X energy saving when sacrificing 8.35 dB output quality.

Similar content being viewed by others

References

Abdallah, R., & Shanbhag, N. (2009). Error-resilient low-power viterbi decoder architectures. IEEE Transactions on Signal Processing, 57(12), 4906–4917.

Bhushan, M., Ketchen, M.B., Polonsky, S., & Gattiker, A. (2006). Ring oscillator based technique for measuring variability statistics. In IEEE Int. Conf., Microelectron. Test Struct. 2006. ICMTS 2006. pp. 87–92. doi:10.1109/ICMTS.2006.1614281.

Bowman, K.A., Tschanz, J.W., Kim, N.S., Lee, J.C., Wilkerson, C.B., Lu, S.L., Karnik, T., & De, V.K. (2009). Energy-efficient and metastability-immune resilient circuits for dynamic variation tolerance. IEEE Journal on Solid-State Circuits, 44(1), 49–63.

Calhoun, B.H., & Chandrakasan, A.P. (2004). Standby power reduction using dynamic voltage scaling and canary flip-flop structures. IEEE J on Solid-State Circuits, 39(9), 1504–1511. doi:10.1109/JSSC.2004.831432.

Choudhury, M., Chandra, V., Mohanram, K., & Aitken, R. (2010). TIMBER: Time borrowing and error relaying for online timing error resilience. In Des. Autom. Test Eur. Conf. Exhib. (DATE), 2010, pp. 1554–1559. doi:10.1109/DATE.2010.5457058.

De Man, H. (2005). Ambient intelligence: gigascale dreams and nanoscale realities. In Solid-State Circuits Conf. 2005. Dig. Tech. Pap. ISSCC. 2005 IEEE Int., pp. 29–35. IEEE.

Ernst, D., Kim, N.S., Das, S., Pant, S., Rao, R., Pham, T., Ziesler, C., Blaauw, D., Austin, T., Flautner, K., & Mudge, T. (2003). Razor: a low-power pipeline based on circuit-level timing speculation. In Microarchitecture, 2003. MICRO-36. Proceedings. 36th Annu. IEEE/ACM Int. Symp., pp. 7–18. doi:10.1109/MICRO.2003.1253179.

Fojtik, M., Fick, D., Kim, Y., Pinckney, N., Harris, D.M., Blaauw, D., & Sylvester, D. (2013). Bubble Razor: Eliminating timing margins in an ARM cortex-M3 processor in 45 nm CMOS using architecturally independent error detection and correction. IEEE Journal on Solid-State Circuits, 48(1), 66–81. doi:10.1109/JSSC.2012.2220912.

Hegde, R., & Shanbhag, N.R. (1999). Energy-efficient signal processing via algorithmic noise-tolerance. In Proceedings 1999 Int. Symp., Low Power Electron. Des. 1999. pp. 30–35.

Huang, Y., Li, M., Li, C., Debacker, P., & Perre, L.V.D. (2014). Computation-Skip Error Resilient Scheme for Recursive CORDIC. In 2014 SIPS, Work. Signal Process. Syst. Press.

Kao, J.T., Miyazaki, M., & Chandrakasan, A.P. (2002). A 175-MV multiply-accumulate unit using an adaptive supply voltage and body bias architecture. IEEE Journal on Solid-State Circuits, 37(11), 1545–1554. doi:10.1109/JSSC.2002.803957.

Kim, E.P., & Shanbhag, N.R. (2012). Energy-efficient LDPC decoders based on error-resiliency. 2012 IEEE Workshop on Signal Processing System, 149–154. doi:10.1109/SiPS.2012.60..

Kuhn, K.J. (2010). CMOS transistor scaling past 32nm and implications on variation. In 2010 IEEE/SEMI, Adv. Semicond. Manuf. Conf. (ASMC), pp. 241–246. doi:10.1109/ASMC.2010.5551461.

Li, C., Bourdoux, A., Verhelst, M., Huang, Y., Li, M., Van Der Perre, L., & Pollin, S. (2015). lt;30 mW rectangular-to-polar conversion processor in 802.11ad polar transmitter. In 2015 IEEE Int. Conf., Acoust. Speech Signal Process. (ICASSP), pp. 1022–1026. doi:10.1109/ICASSP.2015.7178124.

Li, C., Li, M., Khalaf, K., Bourdoux, A., Verhelst, M., Ingels, M., Wambacq, P., Craninckx, J., Van Der Perre, L., & Pollin, S. (2015). Opportunities and challenges of digital signal processing in deeply technology-scaled transceivers. Journal of Signal Processing System, 78(1), 5–19.

Shin, I., Kim, J.j., Lin, Y.s., & Shin, Y. (2013). Architecture with 1-Cycle Timing Error for Low Voltage Operations Correction for Low Voltage Operations. In 2013 IEEE Int. Symp., Low Power Electron. Des. (ISLPED), vol. 3, pp. 199–204.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Huang, Y., Li, M., Li, C. et al. Computation-skip Error Mitigation Scheme for Power Supply Voltage Scaling in Recursive Applications. J Sign Process Syst 84, 413–424 (2016). https://doi.org/10.1007/s11265-015-1096-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-015-1096-z