Abstract

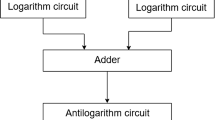

This paper proposes a high-throughput and low-complexity decoder (D_LBAC) based on Logarithmic Binary Arithmetic Coding (LBAC). It can easily implement multiple symbols decoding. The proposed scheme does not use multiplication and division operations nor look up tables (LUTs). It has a simple algorithm structure and only requires additions and shift operations. Experimental results show that it has about 0.2–0.7 % bit-rate savings and can decode 3.5 symbols per cycle on average. The hardware implementation design described in this paper can achieve a high symbol processing capability and the lower hardware costs.

Similar content being viewed by others

References

ITU-T and ISO/IEC JTC 1. (2000). JPEG2000 image coding system: core coding system. ITU-T Recommendation T.800 and ISO/IEC 15444–1.

Howard, P. G., Kossentini, F., Martins, B., Forchhammer, S., & Rucklidge, W. J. (2002). The emerging JBIG2 standard. IEEE Transactions on Circuits and Systems for Video Technology, 8(7), 838–848.

Sze, V., & Budagavi, M. (2012). Overview of the high efficiency video coding (HEVC) standard. IEEE Transactions on Circuits and Systems for Video Technology, 22(12), 1649–1668.

AVS Video Expert Group, Information Technology - Advanced Audio Video Coding Standard Part 2: Video, in Audio Video Coding Standard Group of China (AVS+), GY/T257.1-2012.

Witten, I. H., Neal, R. M., & Cleary, J. H. (1987). Arithmetic coding for data compression. Communications of the ACM, 30(60), 520–540.

Marpe, D., Schwarz, H., & Wiegand, T. (2003). Context-based adaptive binary arithmetic coding in H.264/AVC video compression standard. IEEE Transactions on CSVT, 13(7), 620–636.

Mitchell, J.L., Penebaker, W.B. & Goertzel, G. (1988). Log encoder/decoder system. U. S. Patent 4791403.

Hong, D., & Eleftheriadis, A. (2007). Memory--efficient semi-quasi renormalization for arithmetic coding. IEEE Transactions on Circuits and Systems for Video Technology, 17(1), 106–110.

Sze, V., & Budagavi, M. (2012). High throughput CABAC entropy coding in HEVC. Circuits and Systems for Video Technology, IEEE Transactions, 22(12), 1778–1791.

Budagavi, M., & Demircin, M. U. (2010). Parallel context processing techniques for high coding efficiency entropy coding in HEVC. Geneva: JCTVC-B088, 2nd Meeting.

Sugimoto, K., Minezawa, A., Sekiguchi, S., Asai, K., & Murakami, T. (2012). Reduction of initialization tables for CABAC contexts. Input Document to JCT-VC JCTVC-H0646.

Yu, W., Yang, P. & He, Y. (2006). Arithmetic coding on logarithm domain. PCS.

1857–2013 -IEEE standard for advanced audio and video coding.

HM16.3, Available: https://hevc.hhi.fraunhofer.de/svn/svn HEVCSoftware/tags/HM-16.3/.

ISO/IEC-FCT1/SC29/WG11. (2012). Common test conditions and software reference configurations. Geneva: JCTVC-I1100.

Yu, Q., Yu, W., Yang, P., Zheng, J., Zheng, X., & He, Y. (2015). An efficient adaptive binary arithmetic coder based on logarithmic domain. Image Processing, IEEE Transactions, 24(11), 4225–4239.

Osorio, R.R., & Bruguera, J.D. (2004). Arithmetic coding architecture for H.264/AVC CABAC compression system, Digital System Design.

Kuang, S.-R., Jou, J.-M., & Chen, Y.-L. (2002). The design of an adaptive on-line binary arithmetic-coding chip. IEEE Transactions on Circuits and Systems, 45(7), 693–706.

Di, W., Wen, G., Mingzeng, H., & Zhenzhou J. (2003). A VLSI architecture design of CAVLC Decoder. Proc. 5th International Conference on ASIC, 2, 962–965.

Yu, Q. (2014). Improvements of AEC engine. Audio Video Coding Working Group.

Bjontegaard G. (2001). Calculation of average PSNR differences between RD curves. ITU-T, Austin, TX, Tech. Rep. SC16/Q6.

Acknowledgments

The authors would like to thank the associate editor and the reviewers for their time, comments and prompt responses. This work is partially supported by the National project of 863 2015AA015903 and National project of 973 2009CB320903.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Yu, Q., Yu, W., Zheng, J. et al. A High-Throughput and Low-Complexity Decoding Scheme based on Logarithmic Domain. J Sign Process Syst 88, 245–257 (2017). https://doi.org/10.1007/s11265-016-1143-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-016-1143-4