Abstract

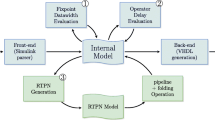

It is important to verify the absence of deadlocks in asynchronous circuits. Much previous work relies on a reachability analysis of the circuits’ states, with the use of binary decision diagrams (BDDs) or Petri nets to model the behaviors of circuits. This paper presents an alternative approach focusing on the structural properties of well-formed asynchronous circuits that will never suffer deadlocks. A class of data-driven asynchronous pipelines is targeted in this paper, which can be viewed as a network of basic components connected by handshake channels. The sufficient and necessary conditions for a component network consisting of Steer, Merge, Fork and Join are given. The slack elasticity of the channels is analyzed in order to introduce pipelining. As an application, a deadlock checking method is implemented in a syntax-directed asynchronous design tool — Teak. The proposed method shows a great runtime advantage when compared against previous Petri net based verification tools.

Similar content being viewed by others

References

Edwards D, Bardsley A. Balsa: An asynchronous hardware synthesis language. The Computer Journal, 2002, 45(1): 12-18.

van Berkel K. Handshake Circuits: An Asynchronous Architecture for VLSI Programming. 1st edition, Cambridge University Press, 1993.

Brunvand E, Sproull R F. Translating concurrent programs into delay-insensitive circuits. In Proc. the 7th International Conference on Computer-Aided Design, Santa Clara, USA, November 5–9, 1989, pp.262-265.

Queille J P, Sifakis J. Specification and verification of concurrent systems in CESAR. In Proc. the 5th International Symposium on Programming, Turin, Italy, April 6–8, 1982, pp.337-350.

Clarke E M, Emerson E A. Design and synthesis of synchronization skeletons using branching time temporal logic. Logics of Programs, 1982, 131(3): 52–71.

Burch J R, Clarke E M, Long D E, McMillan K L, Dill D L. Symbolic model checking for sequential circuit verification. IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, 1994, 13(4): 401–424.

Bryant R E. Graph-based algorithms for boolean function manipulation. IEEE Trans. Computers, 1986, 35(8): 677-691.

McMillan K L. Using unfoldings to avoid the state explosion problem in the verification of asynchronous circuits. In Proc. the 4th Workshop on Computer Aided Verification, Montreal, Canada, June 29-July 1, 1992, pp.164-177.

Murata T. Petri nets: Properties, analysis and applications. Proceedings of the IEEE, 1989, 77(4): 541–580.

Roig O, Cortadella J, Pastor E. Verification of asynchronous circuits by BDD-based model checking of Petri nets. In Proc. the 16th International Conference on Application and Theory of Petri Nets, Turin, Italy, June 26–30, 1995, pp.374-391.

Melzer S, Römer S. Deadlock checking using net unfoldings. In Proc. the 9th International Conference on Computer Aided Verification, Haifa, Israel, June 22–25, 1997, pp.352-363.

Khomenko V, Koutny M. LP deadlock checking using partial order dependencies. In Proc. the 11th International Conference on Concurrency Theory, Pennsylvania, USA, August 22–25, 2000, pp.410-425.

Poliakov I, Mokhov A, Rafiev A, Sokolov D, Yakovlev A. Automated verification of asynchronous circuits using circuit Petri nets. In Proc. the 14th International Symposium on Asynchronous Circuits and Systems, Newcastle, UK, April 7–10, 2008, pp.161-170.

McMillan K L. A technique of state space search based on unfolding. Formal Methods in System Design, 1995, 6(1): 45–65.

Bruno J, Altman S M. A theory of asynchronous control networks. IEEE Trans. Computers, 1971, 20(6): 629–638.

Manohar R, Martin A J. Slack elasticity in concurrent computing. In Proc. the 4th International Conference on the Mathematics of Program Construction, Marstrand, Sweden, June 15–17, 1998, pp.272-285.

Bardsley A, Tarazona L, Edwards D. Teak: A token-flow implementation for the Balsa language. In Proc. the 9th International Conference on Application of Concurrency to System Design, Augsburg, Germany, July 1–3, 2009, pp.23-31.

Sparsø J, Furber S. Principles of Asynchronous Circuit Design — A Systems Perspective, Kluwer Academic Publishers, 2001.

Beerel P A, Kim N H, Lines A, Davies M. Slack matching asynchronous designs. In Proc. the 12th International Symposium on Asynchronous Circuits and Systems, Grenoble, France, March 13–15, 2006, pp.184-194.

Prakash P, Martin A J. Slack matching quasi delay-insensitive circuits. In Proc. the 12th International Symposium on Asynchronous Circuits and Systems, Grenoble, France, March 13–15, 2006, pp.195-204.

Gill G, Gupta V, Singh M. Performance estimation and slack matching for pipelined asynchronous architectures with choice. In Proc. the 45th International Conference on Computer-Aided Design, San Jose, USA, November 10–13, 2008, pp.449-456.

Tarjan R E. Enumeration of the elementary circuits of a directed graph. SIAM Journal on Computing, 1973, 2: 211–216.

Khomenko V. Punf documentation and user guide manual, Version 6.03, 2003.

Khomenko V. A usable reachability analyser, CS-TR-1140, Newcastle Univ., http://homepages.cs.ncl.ac.uk/victorkhomenko/tods/mpsat/CS-TR-1140.pdf, 2009.

The SPARC architecture manual (Version 9), SPARC International, Inc., Weaver D L, Germond T (eds.), http://www.sparc.com/standards/SPARCV9.pdf, 1994.

Author information

Authors and Affiliations

Corresponding author

Additional information

This work was supported by the National Natural Science Foundation of China under Grant Nos. 60873015, 61070037, and 61103016.

Electronic Supplementary Material

Below is the link to the electronic supplementary material.

Rights and permissions

About this article

Cite this article

Ren, HG., Wang, ZY. & Edwards, D. Structure-Based Deadlock Checking of Asynchronous Circuits. J. Comput. Sci. Technol. 26, 1031–1040 (2011). https://doi.org/10.1007/s11390-011-1199-3

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11390-011-1199-3