Abstract

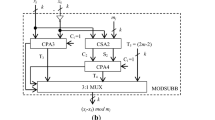

Residue number system (RNS) has received considerable attention since decades before, because it has inherent carry-free and parallel properties in addition, subtraction, and multiplication operations. For an odd moduli set, the fundamental problems in RNS, such as number comparison, sign determination, and overflow detection, can be solved based on parity checking. The paper proposes a parity checking algorithm along with related propositions and the certification based on the celebrated Chinese remainder theory (CRT) and mixed radix conversion (MRC) for the moduli set {2n − 1, 2n + 1, 22n + 1}. The parity checker consists of two modular adders and a carry-look-ahead chain. The hardware implementation requires less area and path delay. Besides, the implementations of number comparison, sign determination, and overflow detection, which are based on this parity checker, are also performed in this paper. And this kind of parity checker can be used as a basic element to design ALUs and DSP module in RNS.

Similar content being viewed by others

References

Dally W J, Lacy S. VLSI architecture: past, present, and future. In: Proceedings of the 20th Anniversary Conference on Advanced Research in VLSI. New York: IEEE, 1999. 232–241

Liu Y, Lai E M K. Design and implementation of a RNS-based 2-D DWT processor. IEEE Trans Consum Electr, 2004, 50(1): 376–385

Lindahl A, Bengtsson L. A low-power FIR filter using combined residue and radix-2 signed-digit representation. In: Proceedings of the 8th Euromicro Conference on Digital System Design (DSD’05). New York: IEEE, 2005. 42–47

Yang L L, Hanzo L. A residue number system based parallel communication scheme using orthogonal signaling: part I-system outline. IEEE Trans Veh Tech, 2002, 51(6): 1534–1546

Wang W, Swamy M N S, Ahamad M O. RNS application for digital image processing. In: Proceedings of the 4th IEEE International Workshop on System-on-Chip for Real-Time Applications (IWSOC’04). New York: IEEE, 2004. 77–80

Lu M, Chiang J S. A novel division algorithm for the residue number system. IEEE Trans Comput, 1992, 41(8): 1026–1032

Burgess N. Scaling an RNS number using the core function. In: Proceedings of the 16th IEEE Symposium on Computer Arithmetic. New York: IEEE, 2003. 262–269

Suk J H, Youn J S, Kim H G, et al. A parity checker for a large residue numbers based Montgomery reduction method. IEICE Trans Electron, 2005, E88-C(9): 1880–1885

Wang W, Swamy M N S, Omair A M, et al. A study of the residue-to-binary converters for the three-moduli sets. IEEE Trans Circuits-I, 2003, 50(2): 235–243

Wang W, Swamy M N S, Ahmad M O, et al. A parallel residue-to-binary converter for the moduli set \( \{ 2^m - 1,2^{2^0 m} + 1,2^{2^1 m} + 1, \ldots ,2^{2^k m} + 1\} \). VLSI Des, 2002, 14(2): 183–191

Efstathiou C. Fast parallel-prefix modulo 2n+1 adders. IEEE Trans Comput, 2004, 53(9): 1211–1216

Patel R A, Benaissa M, Powell N, et al. ELMMA: a new low power high-speed adder for RNS. SIPS, 2004, 95–100

Hiasat A A. High-speed and reduced-area modular adder structures for RNS. IEEE Trans Comput, 2002, 51(1): 84–89

Wang Y K. New Chinese remainder theorems. In: Proceedings of the 32nd Asilomar Conference Signals, Systems, Computers. New York: IEEE, 1998. 165–171

Wang W, Swamy M N S, Ahmad M O, et al. A high-speed residue-to-binary converter for three-moduli (2k, 2k−1, 2k−1−1) RNS and a scheme for its VLSI implementation. IEEE Trans Circuits-II, 2000, 47(12): 1576–1581

Dimauro G, Impedovo S, Pirlo G. A new technique for fast number comparison in the residue number system. IEEE Trans Comput, 1993, 42(5): 608–612

Wang Y K. A new algorithm for RNS magnitude comparison based on new Chinese remainder theorem II. In: Proceedings of the 9th Great Lakes Symposium on VLSI table of contents. New York: IEEE, 1999. 362–365

Setiaarif E, Siy P. A new moduli set selection technique to improve sign detection and number comparison in residue number system (RNS). In: Annual Meeting of the North American Fuzzy Information Processing Society(NAFIPS 2005). New York: IEEE, 2005. 766–768

Abtahi M, Siy P. The non-linear characteristic of core function of RNS numbers and its effect on RNS to binary conversion and sign detection algorithms. In: NAFIPS 2005–2005 Annual Meeting of the North American Fuzzy Information Processing Society. New York: IEEE, 2005. 731–736

Cardarilli G C, Nannarelli A, Re M. Programmable power-of-two RNS scaler and its application to a QRNS polyphase filter. In: Proceedings of 2005 IEEE International Symposium on Circuits and Systems (ISCAS). Kobe: IEEE, 2005. 1002–1005

Rao T R N, Trehan A K. Binary logic for residue arithmetic using magnitude index. IEEE Trans Comput, 1970, C-19(8): 752–757

Sasaki A. The basis for implementation of additive operations in the residue number system. IEEE Trans Comput, 1968, C-17(11): 1066–1073

Author information

Authors and Affiliations

Corresponding author

Additional information

Supported by the National Natural Science Foundation of China (Grant No. 60496313)

Rights and permissions

About this article

Cite this article

Ma, S., Hu, J., Zhang, L. et al. An efficient RNS parity checker for moduli set {2n − 1, 2n + 1, 22n + 1} and its applications. Sci. China Ser. F-Inf. Sci. 51, 1563–1571 (2008). https://doi.org/10.1007/s11432-008-0097-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11432-008-0097-y