Abstract

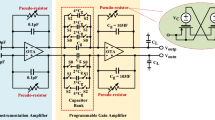

A low offset, low noise chopper amplifier for sensor system application is presented. Low 1/f noise is achieved by employing chopper technique, and low offset is achieved by employing residual offset suppression circuit. The open-loop gain is extended using three-stage nested Miller configuration. The chip was implemented in 0.5 μm 2P3M CMOS process. The amplifier is featured by an open-loop gain of 135 dB and a GBW of 3 MHz. The measured offset voltage is 3 μV, and the equivalent input noise power spectrum density at 1 Hz is 96 nV / \(\sqrt {Hz} \).

Similar content being viewed by others

References

Yin T, Yang H G, Liu K. A low-noise, low-offset chopper amplifier for micro-sensor readout circuit. Chin J Semiconduct, 2007, 28: 796–801

Enz C C, Temes G C. Circuit techniques for reducing the effects of op-amp imperfections: autozeroing, correlated double sampling, and chopper stabilization. Proc IEEE, 1996, 84: 1584–1614

Chinwuba D E, Johan P V, Xing X Y, et al. A 6.7 nV / \(\sqrt {Hz} \) Sub-MHz-1/f-Corner 14 b analog-to-digital interface for rail-to-rail precision voltage sensing. In: Proceedings of International Solid-State Circuits Conference, San Francisco, 2011. 246–248

Laville S, Pontarollo S, Dufaza C, et al. Integrated offset trimming technique. In: Proceedings of the 27th European Solid-State Circuits Conference, Villach, 2001. 89–92

Witte J F, Makinwa K A, Huijsing J H. Dynamic Offset Compensated CMOS Amplifier. Springer, 2009. 2–3

Witte J F, Huijsing J H, Makinwa K A. A current-feedback instrumentation amplifier with 5 μV offset for bidirectional high-side current-sensing. In: Proceedings of International Solid-State Circuits Conference, San Francisco, 2008. 574–596

Hu Y, Sawan M. CMOS front-end amplifier dedicated to monitor very low amplitude signal from implantable sensors. Analog Integr Circuit Signa Process, 2002, 33: 29–41

Enz C C, Vittoz E A, Krummenacher F. A CMOS chopper amplifier. IEEE J Solid-State Circuits, 1987, 22: 335–342

Bakker A, Huiijsing J H. High-accuracy CMOS smart temperature sensors. Kluwer, 2000. 23–25

Menolfi C, Huang Q. A chopper modulated instrumentation amplifier with first order low-pass filter and delayed modulation scheme. In: Proceedings of the 25th European Solid-State Circuits Conference, Duisberg, 1999. 54–57

Menolfi C, Huang Q. A low-noise CMOS instrumentation amplifier for thermoelectric infrared detectors. IEEE J Solid-State Circuits, 1997, 32: 968–976

Wu S T, Lin F, Guo D H, et al. Design of CMOS operating amplifier for eliminating DC offset based on chopper technology. Semiconduct Technol, 2003, 28: 60–64

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Huang, Z., Wang, W., Jiang, F. et al. A low offset chopper amplifier with three-stage nested Miller configuration. Sci. China Inf. Sci. 57, 1–7 (2014). https://doi.org/10.1007/s11432-013-4903-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11432-013-4903-9