Abstract

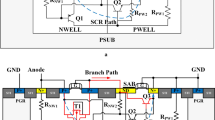

A conventional diode-triggered silicon-controlled rectifier (DTSCR) structure with a layout strategy for electrostatic discharge (ESD) protection is presented and confirmed in a 65-nm CMOS technology. The modified device is featured by a scaled-down trigger-diode string, which shortens its turn-on time using a variable scaling factor. To confirm the parasitic resistance adjustments of the modified DTSCR, transmission line pulsing (TLP)/very fast transmission line pulsing (VF-TLP) tests and simulations are performed on the device. Compared to a conventional DTSCR, this structure exhibits an improved turn-on speed and robustness, which are suitable for I/O protection of ESD events in the nanosecond range, particularly the charged-device model (CDM) event.

Similar content being viewed by others

References

Ker M D, Lin C Y. ESD protection consideration in nanoscale CMOS technology. In: Proceedings of IEEE International Conference on Nanotechnology, Portland, 2011. 720–723

Cao J, Xu J Y, Wang Y, et al. A compact SCR model using advanced BJT models and standard SPICE elements. Sci China Inf Sci, 2016, 59: 109302

Yin L, Shen L, Jiang H, et al. Impact of self-heating effects on nanoscale Ge p-channel FinFETs with Si substrate. Sci China Inf Sci, 2018, 61: 062401

Yang C, Luo X, Deng S, et al. High-voltage trench-gate hole-gas enhancement-mode HEMT with multi-conduction channels. Sci China Inf Sci, 2018, 61: 062402

Zhou Q, Han Y, Zhang S F, et al. A low power V-band LC VCO with high Q varactor technique in 40 nm CMOS process. Sci China Inf Sci, 2017, 60: 089401

Ma F, Han Y, Dong S R, et al. Improved low-voltage-triggered SCR structure for RF-ESD protection. IEEE Electron Device Lett, 2013, 34: 1050–1052

Lin C Y, Ker M D, Meng G X. Low-capacitance and fast turn-on SCR for RF ESD protection. IEICE Trans Electron, 2008, E91C: 1321–1330

Song B, Han Y, Dong S R, et al. Compact MOS-triggered SCR with faster turn-on speed for ESD protection. Microelectron Reliab, 2010, 50: 1393–1397

Chen W Y, Rosenbaum E, Ker M D. Diode-triggered silicon-controlled rectifier with reduced voltage overshoot for CDM ESD protection. IEEE Trans Device Mater Relib, 2012, 12: 10–14

Zhang P, Wang Y, Zhang X, et al. Novel silicon-controlled rectifier (SCR) for digital and high-voltage ESD power supply clamp. Sci China Inf Sci, 2014, 57: 029401

Li J J, Sarro J D, Li Y, et al. Investigation of SOI SCR triggering and current sustaining under DC and TLP conditions. In: Proceedings of Electrical Overstress/Electrostatic Discharge Symposium, Las Vegas, 2013. 1–6

Zhang L Z, Wang Y, He Y D. Structure-dependent behaviors of diode-triggered silicon controlled rectifier under electrostatic discharge stress. Chin Phys B, 2016, 25: 128501

Mishra R, Li J J, Sarro J D, et al. Effect of embedded-SiGe (eSiGe) on ESD TLP and VFTLP characteristics of diode-triggered silicon controlled rectifiers (DTSCRs). In: Proceedings of Electrical Overstress/Electrostatic Discharge Symposium, Tucson, 2012. 1–5

Ginawi A, Xia T, Gauthier R. Reducing the turn-on time and overshoot voltage for a diode-triggered silicon-controlled rectifier during an electrostatic discharge event. In: Proceedings of IEEE International System-on-chip Conference, Las Vegas, 2014. 109–114

Mergens M P J, Russ C C, Verhaege K G, et al. Speed optimized diode-triggered SCR (DTSCR) for RF ESD protection of ultra-sensitive IC nodes in advanced technologies. IEEE Trans Device Mater Relib, 2005, 5: 532–542

Sarro J D, Chatty K, Gauthier R, et al. Study of design factors affecting turn-on time of silicon controlled rectifiers (SCRS) in 90 and 65 nm bulk CMOS technologies. In: Proceedings of IEEE Reliability Physics Symposium, Phoenix, 2006. 163–168

Brennan C J, Chang S H, Woo M, et al. Implementation of diode and bipolar triggered SCRs for CDM robust ESD protection in 90 nm CMOS ASICs. Microelectron Reliab, 2007, 47: 1030–1035

Gauthier R, Abou-Khalil M, Chatty K, et al. Investigation of voltage overshoots in diode triggered silicon controlled rectifiers (DTSCRs) under very fast transmission line pulsing (VFTLP). In: Proceedings of Electrical Overstress/ Electrostatic Discharge Symposium, Anaheim, 2009. 1–10

Miao M, Dong S R, Wu J, et al. Minimizing multiple triggering effect in diode-triggered silicon-controlled rectifiers for ESD protection applications. IEEE Electron Device Lett, 2012, 33: 893–895

Shrivastava M, Baghini M S, Sharma D K, et al. A novel bottom spacer FinFET structure for improved short-channel, power-delay, and thermal performance. IEEE Trans Electron Dev, 2010, 57: 1287–1294

Acknowledgements

This work was supported by National Natural Science Foundation of China (Grant No. 61774005) and Beijing Natural Science Foundation (Grant No. 4162030).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Zhang, L., Wang, Y., Wang, Y. et al. Improved turn-on behavior in a diode-triggered silicon-controlled rectifier for high-speed electrostatic discharge protection. Sci. China Inf. Sci. 62, 62402 (2019). https://doi.org/10.1007/s11432-017-9427-1

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11432-017-9427-1