Abstract

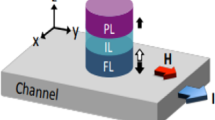

In order to realize high efficient magnetization switching in magnetic tunnel junction (MTJ), several potential mechanisms have been realized as the interplay effect to MTJ device, such as the interaction between spin orbit torque-spin transfer torque (STT) and voltage-controlled magnetic anisotropy (VCMA)-STT. The interplay mechanisms have been experimentally explored with improved switching energy efficiency comparing with traditional STT method. Considering the requirement of mixed-precision memory, we propose a novel write-only in-memory computing paradigm based on interplay bitwise operation in two terminal or three terminal MRAM bit-cell, which aims to reduce the layout overhead of peripheral computing circuits, as well as to eliminate read decision failure in the procedure of in-memory computing. Specifically, the proposed write-only bitwise in-memory computing is demonstrated with OR, AND, XOR, full adder operations. Four nonvolatile approximate full adders (AxFAs) are proposed and implemented in different MRAM bit-cells. The AxFAs can be easily reconfigured into memory units with simple connections. Image processing applications are used to demonstrate the in-memory computing, include FA, XOR operation. Comparing with traditional sensing based approach, more than 80% energy reduction is obtained using the proposed interplay writing-only in memory computing with approximation setup. A 61.4% energy reduction is achieved using VCMA mechanism interaction based XOR functions.

Similar content being viewed by others

References

Amiri, P.K., Alzate, J.G., Cai, X.Q., Ebrahimi, F., Hu, Q., Wong, K., Grzes, C., Lee, H., Yu, G., Li, X., Akyol, M., Shao, Q., Katine, J.A., Langer, J., Ocker, B., Wang, K.L.: Electric-field-controlled magnetoelectric RAM: Progress, challenges, and scaling. IEEE Trans. Magn. 51(11), 1–7 (2015)

Angizi, S., Sun, J., Zhang, W., Fan, D., Graphs: a graph processing accelerator leveraging SOT-MRAM. In: Design. Automation Test in Europe Conference Exhibition (DATE), pp. 378–383 (2019)

Angizi, S., He, Z., Awad, A., Fan, D.: Mrima: An MRAM-based in-memory accelerator. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 39(5), 1123–1136 (2020)

Baek, S., Park, K., Kil, D., Jang, Y., Park, J., Lee, K., Park, B.: Complementary logic operation based on electric-field controlled spinorbit torques. Nat. Electron. 1(7), 388–403 (2018)

Cai, H., Wang, Y., Naviner, L., Zhao, W.: Robust ultra-low power non-volatile logic-in-memory circuits in FD-SOI technology. IEEE Trans. Circuits Syst. I Regul. Pap. 64(4), 847–857 (2017)

Dong, X., et al.: Nvsim: A circuit-level performance, energy, and area model for emerging non-volatile memory. In: In emerging memory technologies, pp. 15–50. Springer, New York (2014)

Frustaci, F., Blaauw, D., Sylvester, D., Alioto, M.: Approximate SRAMs with dynamic energy-quality management. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 24(6), 2128–2141 (2016)

Frustaci, F., Blaauw, D., Sylvester, D., Alioto, M.: Approximate SRAMs with dynamic energy-quality management, IEEE Trans. Very Large Scale Integr. VLSI Syst. 24(6), 2128–2141 (2016)

Jain, S., Ranjan, A., Roy, K., Raghunathan, A.: Computing in memory with spin-transfer torque magnetic RAM. IEEE Trans. Very Large Scale Integr. VLSI Syst. 26(3), 470–483 (2018)

Kanai, S., Yamanouchi, M., Ikeda, S., Nakatani, Y., Matsukura, F., Ohno, H.: Electric field-induced magnetization reversal in a perpendicular-anisotropy CoFeB-MgO magnetic tunnel junction. Appl. Phys. Lett. 101(12), 122403 (2012)

Kanai, S., Nakatani, Y., Yamanouchi, M., Ikeda, S., Sato, H., Matsukura, F., Ohno, H.: Magnetization switching in a CoFeB/MgO magnetic tunnel junction by combining spin-transfer torque and electric field-effect. Appl. Phys. Lett. 104(21), 212406 (2014)

Le Gallo, M., Sebastian, A., Mathis, R., Manica, M., Giefers, H., Tuma, T., Bekas, C., Curioni, A., Eleftheriou, E.: Mixed-precision in-memory computing. Nat. Electron. 1(4), 246–253 (2018)

Li, S., Xu, C., Zou, Q., Zhao, J., Lu, Y., Xie, Y.: Pinatubo: A processing-in-memory architecture for bulk bitwise operations in emerging non-volatile memories, In: 2016 53nd ACM/EDAC/IEEE Design Automation Conference (DAC), pp. 1–6 (2016)

Liang, J., Han, J., Lombardi, F.: New metrics for the reliability of approximate and probabilistic adders. IEEE Trans. Comput. 62(9), 1760–1771 (2013)

Locatelli, N., Vincent, A.F., Querlioz, D.: Use of magnetoresistive random-access memory as approximate memory for training neural networks. In: 2018 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS), pp. 553–556 (2018)

Maruyama, T., Shiota, Y., Nozaki, T., Ohta, K., Toda, N., Mizuguchi, M., Tulapurkar, A., Shinjo, T., Shiraishi, M., Mizukami, S., Ando, Y., Suzuki, Y.: Large voltage-induced magnetic anisotropy change in a few atomic layers of iron. Nat. Nanotechnol. 4, 158–161 (2009)

Mittal, S.: A survey of techniques for approximate computing. ACM Comput. Surv. 48(4), 62:1–62:33 (2016)

Monazzah, A.M.H., Shoushtari, M., Miremadi, S.G., Rahmani, A.M., Dutt, N.: QuARK: Quality-configurable approximate STT-MRAM cache by fine-grained tuning of reliability-energy knobs. In: 2017 IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), pp. 1–6 (2017)

Natsui, M., Suzuki, D., Sakimura, N., Nebashi, R., Tsuji, Y., Morioka, A., Sugibayashi, T., Miura, S., Honjo, H., Kinoshita, K., Ikeda, S., Endoh, T., Ohno, H., Hanyu, T.: Nonvolatile logic-in-memory LSI using cycle-based power gating and its application to motion-vector prediction. IEEE J. Solid State Circuits 50(2), 476–489 (2015)

Oboril, F., Shirvanian, A., Tahoori, M.: Fault tolerant approximate computing using emerging non-volatile spintronic memories. In: 2016 IEEE 34th VLSI Test Symposium (VTS) (2016)

Ranjan, A., Venkataramani, S., Fong, X., Roy, K., Raghunathan, A.: Approximate storage for energy efficient spintronic memories. In: 2015 52nd ACM/EDAC/IEEE Design Automation Conference (DAC), pp. 1–6 (2015)

Ranjan, A., Venkataramani, S., Pajouhi, Z., Venkatesan, R., Roy, K., Raghunathan, A.: STAxCache: An approximate, energy efficient STT-MRAM cache. In: Design, Automation Test in Europe Conference Exhibition (DATE), pp. 356–361 (2017)

Sampson, A., Nelson, J., Strauss, K., Ceze, L.: Approximate storage in solid-state memories. In: 2013 46th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), pp. 25–36 (2013)

Spinmodel Library (2015). http://www.spinlib.com/STT_PMA_MTJ.html. Accessed 1 Oct 2015

Teimoori, M.T., Hanif, M.A., Ejlali, A.,Shafique, M.: AdAM: Adaptive approximation management for the non-volatile memory hierarchies. In: 2018 Design, Automation Test in Europe Conference Exhibition (DATE), pp. 785–790 (2018)

Wang, W.-G., Li, M., Hageman, S., Chien, C.L.: Electric-field-assisted switching in magnetic tunnel junctions. Nat. Mater. 11, 64–68 (2012)

Wang, S., Lee, H., Ebrahimi, F., Amiri, P.K., Wang, K.L., Gupta, P.: Comparative evaluation of spin-transfer-torque and magnetoelectric random access memory. IEEE J. Emerg. Sel. Topics Circuits Syst. 6(2), 134–145 (2016)

Wang, L., Kang, W., Ebrahimi, F., Li, X., Huang, Y., Zhao, C., Wang, K.L., Zhao, W.: Voltage-controlled magnetic tunnel junctions for processing-in-memory implementation. IEEE Electron Device Lett. 39(3), 440–443 (2018)

Wang, M., Cai, W., Zhu, D., Wang, Z., Kan, J., Zhao, Z., Cao, K., Wang, Z., Zhang, Y., Zhang, T., Park, C., Wang, J., Fert, A., Zhao, W.: Field-free switching of a perpendicular magnetic tunnel junction through the interplay of spinorbit and spin-transfer torques. Nat. Electron. 1(4), 582–588 (2018a)

Wang, Z., Zhang, L., Wang, M., Wang, Z., Zhu, D., Zhang, Y., Zhao, W.: High-density nand-like spin transfer torque memory with spin orbit torque erase operation. IEEE Electron Device Lett. 39(3), 343–346 (2018b)

Wang, Z., Zhou, H., Wang, M., Cai, W., Zhu, D., Klein, J., Zhao, W.: Proposal of toggle spin torques magnetic RAM for ultrafast computing. IEEE Electron Device Lett. 40(5), 726–729 (2019)

Yamaga,Y., Deguchi,Y., Fukuyama,S., Takeuchi,K.: 5x reliability enhanced 40 nm TaOx approximate-ReRAM with domain-specific computing for real-time image recognition of IoT edge devices. In: 2018 IEEE Symposium on VLSI Technology, pp. 109–110 (2018)

Yesil, S., Akturk, I., Karpuzcu, U.R.: Toward dynamic precision scaling. IEEE Micro 38(4), 30–39 (2018)

Zeinali, B., Karsinos, D., Moradi, F.: Progressive scaled STT-RAM for approximate computing in multimedia applications. IEEE Trans. Circuits Syst. II Express Briefs 65(7), 938–942 (2018)

Zeinali, B., Karsinos, D., Moradi, F.: Progressive scaled STT-RAM for approximate computing in multimedia applications. IEEE Trans. Circuits Syst. II Express Briefs 65(7), 938–942 (2018)

Zhang, H., Kang, W., Wang, L., Wang, K.L., Zhao, W.: Stateful reconfigurable logic via a single-voltage-gated spin hall-effect driven magnetic tunnel junction in a spintronic memory. IEEE Trans. Electron Devices 64(10), 4295–4301 (2017)

Zhao, H., Xue, L., Chi, P., Zhao, J.: Approximate image storage with multi-level cell STT-MRAM main memory. In: IEEE/ACM International Conference on Computer-Aided Design (ICCAD) 2017, pp. 268–275 (2017)

Author information

Authors and Affiliations

Corresponding author

Additional information

This work is funded with National Key R&D Program of China under Grant 2018YFB2202800 and National Natural Science Foundation of China under Grant 61904028.

Rights and permissions

About this article

Cite this article

Cai, H., Jiang, H., Zhou, Y. et al. Interplay Bitwise Operation in Emerging MRAM for Efficient In-memory Computing. CCF Trans. HPC 2, 282–296 (2020). https://doi.org/10.1007/s42514-020-00045-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42514-020-00045-6