Abstract

Physical unclonable function (PUF), a reliable and lightweight physical security primitive for secret key generation and anti-tampering. Strong PUF is an important PUF classification that provides a large “Challenge-Response” pairs (CRP) space for device authentication. However, none of the existing PUF constructions is both machine learning (ML) attack resistant and sufficiently lightweight to fit the low-end internet of things and embedded devices. A lightweight composition PUF design, Shift Register based PUF (SRPUF), is proposed in which the time delay performance is sacrificed to make the PUF structure variable and difficult to derive a stable model. A linear feedback shift register (LFSR) is used to de-synchronized the input challenges and output responses of the SRPUF. The LFSR can be configured dynamically to provide a high entropy source and large enough CRP space. The SRPUF is simulated in Python then implemented on a 28 nm FPGA. The experimental results show that the uniformity and uniqueness of the PUF is 49.8%, 49.9%, which is close to the ideal value, and the hardware overhead is small. Meanwhile, it shows excellent resistance to several popular ML attack methods. This new PUF design idea is suitable for resource-constrained and time delay-insensitive applications.

Similar content being viewed by others

References

Afghah, F., Cambou, B., Abedini, M., Zeadally, S.: A ReRAM physically unclonable function (ReRAM PUF)-based approach to enhance authentication security in software defined wireless networks. Int. J. Wirel. Inf. Netw. 25, 117–129 (2018). https://doi.org/10.1007/s10776-018-0391-6

Aseeri, A., Zhuang, Y., Alkatheiri, M.: A machine learning-based security vulnerability study on XOR PUFs for resource-constraint internet of things. Presented at the July 1 (2018)

Becker, G.T.: The gap between promise and reality: on the insecurity of XOR arbiter PUFs. In: Güneysu, T., Handschuh, H. (eds.) Cryptographic hardware and embedded systems—CHES 2015, pp. 535–555. Springer, Berlin (2015a)

Becker, G.T.: On the pitfalls of using arbiter-PUFs as building blocks. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 34, 1295–1307 (2015b). https://doi.org/10.1109/TCAD.2015.2427259

Bishop, C.M.: Pattern recognition and machine learning. Springer, New York (2006)

Che, W., Saqib, F., Plusquellic, J.: PUF-based authentication. In: 2015 IEEE/ACM international conference on computer-aided design (ICCAD). pp. 337–344 (2015)

Daihyun, L., Lee, J.W., Gassend, B., Suh, G.E., van Dijk, M., Devadas, S.: Extracting secret keys from integrated circuits. IEEE Trans. Very Large Scale Integr. VLSI Syst. 13, 1200–1205 (2005). https://doi.org/10.1109/TVLSI.2005.859470

Delvaux, J.: Machine-learning attacks on PolyPUFs, OB-PUFs, RPUFs, LHS-PUFs, and PUF–FSMs. IEEE Trans. Inf. Forensics Secur. 14, 2043–2058 (2019). https://doi.org/10.1109/TIFS.2019.2891223

Delvaux, J., Peeters, R., Gu, D., Verbauwhede, I.: A survey on lightweight entity authentication with strong PUFs. ACM Comput. Surv. 48, 1–42 (2015). https://doi.org/10.1145/2818186

Deng, D., Wang, Y., Guo, Y.: Novel design strategy towards A2 trojan detection based on built-in acceleration structure. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. (2020). https://doi.org/10.1109/TCAD.2020.2977069

Dubrova, E., Naslund, O., Degen, B., Gawell, A., Yu, Y.: CRC-PUF: a machine learning attack resistant lightweight PUF construction. In: 2019 IEEE European symposium on security and privacy workshops (EuroS&PW). pp. 264–271. IEEE, Stockholm (2019)

Fruhashi, K., Shiozaki, M., Fukushima, A., Murayama, T., Fujino, T.: The arbiter-PUF with high uniqueness utilizing novel arbiter circuit with delay-time measurement. In: 2011 IEEE international symposium of circuits and systems (ISCAS). pp. 2325–2328. IEEE, Rio de Janeiro (2011)

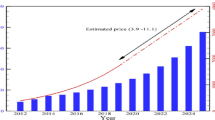

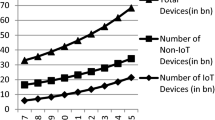

Ganguli, S., Friedman, T.: IoT Technology Disruptions : A Gartner Trend Insight Report What You Need to Know. Technical Report June, Gartner Research (2017)

Gassend, B., Lim, D., Clarke, D., van Dijk, M., Devadas, S.: Identification and authentication of integrated circuits. Concurr. Comput. Pract. Exp. 16, 1077–1098 (2004). https://doi.org/10.1002/cpe.805

Goodfellow, I., Bengio, Y., Courville, A.: Deep learning. The MIT Press, Cambridge (2016)

Gu, C., Cui, Y., Hanley, N., O’Neill, M.: Novel lightweight FF-APUF design for FPGA. In: 2016 29th IEEE international system-on-chip conference (SOCC). pp. 75–80. IEEE, Seattle (2016)

Guajardo, J., Kumar, S.S., Schrijen, G.-J., Tuyls, P.: FPGA intrinsic PUFs and their use for IP protection. In: Paillier, P., Verbauwhede, I. (eds.) Cryptographic hardware and embedded systems—CHES 2007, pp. 63–80. Springer, Berlin (2007)

Hansen, N.: The CMA evolution strategy: a tutorial. ArXiv160400772 Cs Stat. (2016)

He, Z., Wan, M., Deng, J., Bai, C., Dai, K.: A reliable strong PUF based on switched-capacitor circuit. IEEE Trans. Very Large Scale Integr. VLSI Syst. 26, 1073–1083 (2018). https://doi.org/10.1109/TVLSI.2018.2806041

Hori, Y., Kang, H., Katashita, T., Satoh, A., Kawamura, S., Kobara, K.: Evaluation of physical unclonable functions for 28-nm process field-programmable gate arrays. J. Inf. Process. 22, 344–356 (2014). https://doi.org/10.2197/ipsjjip.22.344

Hornik, K.: Approximation capabilities of multilayer feedforward networks. Neural Netw. 4, 251–257 (1991). https://doi.org/10.1016/0893-6080(91)90009-T

Huang, L., Wang, Z., Shen, L., Lu, H., Xiao, N., Liu, C.: A specialized low-cost vectorized loop buffer for embedded processors. In: 2011 Design, Automation Test in Europe. pp. 1–4 (2011)

Ikezaki, Y., Nozaki, Y., Yoshikawa, M.: Deep learning attack for physical unclonable function. In: 2016 IEEE 5th Global Conference on Consumer Electronics. pp. 1–2 (2016)

Kant, S., Kumar, N., Gupta, S., Singhal, A., Dhasmana, R.: Impact of machine learning algorithms on analysis of stream ciphers. In: 2009 Proceeding of international conference on methods and models in computer science (ICM2CS). pp. 251–258 (2009)

Khalafalla, M., Gebotys, C.: PUFs Deep Attacks: Enhanced modeling attacks using deep learning techniques to break the security of double arbiter PUFs. In: 2019 design, automation & test in Europe conference & exhibition (DATE). pp. 204–209. IEEE, Florence (2019)

Kingma, D.P., Ba, J.: Adam: A Method for Stochastic Optimization. ArXiv14126980 Cs. (2017)

Kumar, R., Burleson, W.: On design of a highly secure PUF based on non-linear current mirrors. In: 2014 IEEE international symposium on hardware-oriented security and trust (HOST). pp. 38–43. IEEE, Arlington (2014)

L’Ecuyer, P.: Tables of linear congruential generators of different sizes and good lattice structure. Math. Comput. 68, 249–261 (1999). https://doi.org/10.1090/S0025-5718-99-00996-5

Lao, Y., Yuan, B., Kim, C.H., Parhi, K.K.: Reliable PUF-based local authentication with self-correction. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 36, 201–213 (2017). https://doi.org/10.1109/TCAD.2016.2569581

LeCun, Y., Bengio, Y., Hinton, G.: Deep learning. Nature 521, 436–444 (2015). https://doi.org/10.1038/nature14539

Lee, J.W., Daihyun L., Gassend, B., Suh, G.E., van Dijk, M., Devadas, S.: A technique to build a secret key in integrated circuits for identification and authentication applications. In: 2004 symposium on VLSI circuits. Digest of technical papers (IEEE Cat. No. 04CH37525). pp. 176–179. Widerkehr and Associates, Honolulu (2004)

Lim, D.: Extracting secret keys from integrated circuits, https://dspace.mit.edu/handle/1721.1/18059 (2004)

Liu, J., Yu, Y., Jia, J., Wang, S., Fan, P., Wang, H., Zhang, H.: Lattice-based double-authentication-preventing ring signature for security and privacy in vehicular Ad-Hoc networks. Tsinghua Sci. Technol. 24, 575–584 (2019). https://doi.org/10.26599/TST.2018.9010131

Machida, T., Yamamoto, D., Iwamoto, M., Sakiyama, K.: A New Mode of Operation for Arbiter PUF to Improve Uniqueness on FPGA. Presented at the 2014 federated conference on computer science and information systems, September 29 (2014)

Maes, R., Tuyls, P., Verbauwhede, I.: Intrinsic PUFs from Flip-flops on Reconfigurable Devices. In: 3rd Benelux Workshop on Information and System Security (WIS-Sec2008) (2008)

Mahmoud, A., Rührmair, U., Majzoobi, M., Koushanfar, F.: Combined modeling and side channel attacks on strong PUFs. IACR Cryptol. EPrint Arch. 2013, 632 (2013)

Majzoobi, M., Koushanfar, F., Potkonjak, M.: Lightweight secure PUFs. In: 2008 IEEE/ACM international conference on computer-aided design. pp. 670–673 (2008)

Majzoobi, M., Koushanfar, F., Devadas, S.: FPGA PUF using programmable delay lines. In: 2010 IEEE international workshop on information forensics and security. pp. 1–6. IEEE, Seattle (2010)

Massey, J.: Shift-register synthesis and BCH decoding. IEEE Trans. Inf. Theory. 15, 122–127 (1969). https://doi.org/10.1109/TIT.1969.1054260

Nguyen, P.H., Sahoo, D.P., Jin, C., Mahmood, K., Rührmair, U., Dijk, M. van: The Interpose PUF: Secure PUF Design against State-of-the-art Machine Learning Attacks. IACR Trans. Cryptogr. Hardw. Embed. Syst. 243–290 (2019). https://doi.org/10.13154/tches.v2019.i4.243-290

Pappu, R.: Physical one-way functions. Science 297, 2026–2030 (2002). https://doi.org/10.1126/science.1074376

Rührmair, U., Sehnke, F., S ölter, J., Dror, G., Devadas, S., Schmidhuber, J. ürgen: Modeling attacks on physical unclonable functions. In: Proceedings of the 17th ACM conference on Computer and communications security—CCS ’10. p. 237. ACM Press, Chicago (2010)

Ruhrmair, U., Solter, J., Sehnke, F., Xu, X., Mahmoud, A., Stoyanova, V., Dror, G., Schmidhuber, J., Burleson, W., Devadas, S.: PUF modeling attacks on simulated and silicon data. IEEE Trans. Inf. Forensics Secur. 8, 1876–1891 (2013). https://doi.org/10.1109/TIFS.2013.2279798

Sahoo, D.P., Mukhopadhyay, D., Chakraborty, R.S., Nguyen, P.H.: A multiplexer-based arbiter PUF composition with enhanced reliability and security. IEEE Trans. Comput. 67, 403–417 (2018). https://doi.org/10.1109/TC.2017.2749226

Santikellur, P., Bhattacharyay, A., Chakraborty, R.: Deep learning based model building attacks on arbiter PUF compositions. IACR Cryptol EPrint Arch. (2019)

Shi, J., Lu, Y., Zhang, J.: Approximation attacks on strong PUFs. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. (2019). https://doi.org/10.1109/TCAD.2019.2962115

Suh, G.E., Devadas, S.: Physical unclonable functions for device authentication and secret key generation. In: 2007 44th ACM/IEEE Design Automation Conference. pp. 9–14 (2007)

Tian, Y., Chen, G., Li, J.: On the Design of Trivium. IACR Cryptol. EPrint Arch. 2009, 431 (2009)

Tobisch, J., Becker, G.: On the scaling of machine learning attacks on PUFs with application to noise bifurcation. Presented at the June 23 (2015)

Yashiro, R., Machida, T., Iwamoto, M., Sakiyama, K.: Deep-learning-based security evaluation on authentication systems using arbiter PUF and its variants. In: Ogawa, K., Yoshioka, K. (eds.) Advances in information and computer security, pp. 267–285. Springer International Publishing, Cham (2016)

Ye, J., Hu, Y., Li, X.: OPUF: Obfuscation logic based physical unclonable function. In: 2015 IEEE 21st international on-line testing symposium (IOLTS). pp. 156–161. IEEE, Halkidiki (2015)

Ye, J., Hu, Y., Li, X.: RPUF: Physical unclonable function with randomized challenge to resist modeling attack. In: 2016 IEEE Asian hardware-oriented security and trust (AsianHOST). pp. 1–6 (2016)

Zalivaka, S.S., Puchkov, A.V., Klybik, V.P., Ivaniuk, A.A., Chang, C.-H.: Multi-valued arbiters for quality enhancement of PUF responses on FPGA implementation. In: 2016 21st Asia and South Pacific design automation conference (ASP-DAC). pp. 533–538. IEEE, Macao (2016)

Acknowledgements

This work was supported by the National Natural Science Foundation of China under Grant No 61832018.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

On behalf of all authors, the corresponding author states that there is no conflict of interest.

Rights and permissions

About this article

Cite this article

Hou, S., Deng, D., Wang, Z. et al. A dynamically configurable LFSR-based PUF design against machine learning attacks. CCF Trans. HPC 3, 31–56 (2021). https://doi.org/10.1007/s42514-020-00060-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42514-020-00060-7