Abstract

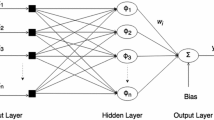

This paper describes how the real-time bandwidth of a radial basis neural network (RBNN) can be improved by the use of a field programmable gate array (FPGA). Accelerated performance is gained by moving the time-consuming RBNN exponential calculations from a general purpose processor to a dedicated FPGA that implements an optimized CORDIC-algorithm. The design methodology is presented and illustrated with a speech recognition application.

Similar content being viewed by others

References

S. Haykin, Neural Networks, Maxwell Macmillan Publishing Company, 1994.

S. Botros and C. Atkeson, “Generalization properties of radial basis functions,” Touretky's Connectionist Summer School, Vol. 3, No.6, pp. 707–713, 1990.

M. Musavi and W. Ahmed, “On the training of radial basis function classifiers,” Neural Networks, Vol. 5, No.10, pp. 595–603, 1992.

A. Saha and J. Keeler, “Algorithms for better representations and faster learning in radial basis function networks,” Touretky's Connectionist Summer School, Vol. 3, No.6, pp. 482–489, 1990.

P. Ienne, T. Cornu, and G. Kuhn, “Special-purpose digital hardware for neural networks: An architectural survey,” Journal of VLSI Signal Processing Systems, No. 13, pp. 5–25, 1996.

R. Kuppuswamy, L. Theogarajan, and L.A. Akers “A programmable Gaussian node,” Proceedings of the IEEE Joint International Conference on Neural Networks, No. 6, pp. 880– 885, 1996.

J.E Volder, “TheCORDICtrigonometric computing technique,” IRE Transactions on Electronics Computers, pp. 330–334, Sept. 1959.

J.S. Walther, “A unified algorithm for elementary functions,” Spring Joint Computer Conference, pp. 379–385, May 1971.

H. Schmid, Decimal Computation, John Wiley & Sons, 1974.

X. Hu, R.G. Harber, and S.C. Bass, “Expanding the range of convergence of the CORDIC algorithm,” IEEE Transactions on Computers, pp. 13–21, Jan. 1991.

S. Kenne and T. Häuser, “Entwicklung einer vollparallelen neuronalen CORDIC-architektur mit Flie{ie217-01}komma-signalprozessor und programmierbaren gate arrays,” Diplomarbeit DT 570, Institut für Datentechnik, 1993.

U. Meyer-Bäse, “Universeller Hilbert-Abtastempfänger mit CORDIC-demodulation,” Funkuhren Zeitsignale Normalfrequenzen, pp. 65–81, 1993.

Y.H. Hu, “The quantization effects of the CORDIC-algorithm,” IEEE Transactions on Signal Processing, pp. 834–844, April 1992.

M. Soderstrand, W. Jenkins, G. Jullien, and F. Taylor, Residue Number System Arithmetic:Modern Applications in Digital Signal Processing, IEEE Press, 1986.

J. Mellott, M. Lewis, F. Taylor, and P. Coffield, “ASAP–A 2D DFT VLSI processor and architecture,” Proc. IEEE ICASSP, Atlanta, 1996.

J. Mellott, J. Smith, and F. Taylor, “The Gauss machine– A Galois-enhanced quadratic residue number system sysotlic array,” Proc. IEEE 11th Symposium on Computer Arithmetic, Windsor, Ontario, pp. 156–162, 1993.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Meyer-Bäse, U., Meyer-Bäse, A., Mellott, J. et al. A Fast Modified CORDIC—Implementation of Radial Basis Neural Networks. The Journal of VLSI Signal Processing-Systems for Signal, Image, and Video Technology 20, 211–218 (1998). https://doi.org/10.1023/A:1008006030955

Published:

Issue Date:

DOI: https://doi.org/10.1023/A:1008006030955