Abstract

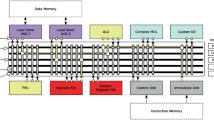

Hybrid architectures combining conventional processors with configurable logic resources enable efficient coordination of control with datapath computation. With integration of the two components on a single device, housekeeping tasks and, optionally, loop control and data-dependent branching, can be handled by the conventional processor, while regular datapath computation occurs on the configurable hardware. This paper describes a novel approach to programming such hybrid devices that gives the programmer control over mapping of data and computation between conventional processor and configurable logic. With a simple set of pragma and intrinsic function directives, the NAPA C language provides for manual control over perhaps the most important aspect of programming such hybrid devices. Alternatively, as experience is gained about tradeoffs between the two computational resources, mapping directives may eventually be generated by an external tool. The paper further describes a research prototype compiler that targets the hybrid processor model, with a concrete implementation for the National Semiconductor NAPA1000 chip. The NAPA C compiler parses the mapping directives, performs semantic analysis, and co-synthesizes a conventional processor executable combined with a configuration bit stream for the configurable logic. Two major compiler phases, the synthesis of pipelined loops and the datapath synthesis, are described in detail.

Similar content being viewed by others

References

R. Razdan and M.D. Smith, “A High-Performance Microarchitecture with Hardware-Programmable Functional Units,” Proceedings of the 27th Annual International Symposium on Microarchitecture, IEEE/ACM, Nov. 1994, pp. 172–180.

R. Wittig and P. Chow, “Onechip: An FPGA Processor with Reconfigurable Logic,” Proceedings of IEEE Symposium on FPGAs for Custom Computing Machines, J.M. Arnold and K.L. Pocek (Eds.), Napa, CA, Apr. 1996.

J.R. Hauser and J. Wawrzynek, “GARP: A MIPS Processor with a Reconfigurable Coprocessor,” Proceedings of IEEE Workshop on FPGAs for Custom Computing Machines, 1997, J. Arnold and K.L. Pocek (Eds.), Napa, CA, Apr., pp. 12–21.

S. Hauck, T. Fry, M. Hosler, and J. Kao, “The Chimera Recon-figurable Functional Unit,” Proceedings of IEEE Symposium on FPGAs for Custom Computing Machines, J.M. Arnold and K.L. Pocek (Eds.), Napa, CA, Apr. 1997, pp. 87–97.

C. Rupp, M. Landguth, T. Garverick, E. Gomersall, H. Holt, J. Arnold, and M. Gokhale, “The Napa Adaptive Processing Architecture,” Proceedings of IEEE Symposium on FPGAs for Custom Computing Machines, J.M. Arnold and K.L. Pocek (Eds.), Napa, CA, Apr. 1998.

M. Rencher and B. Hutchins, “Automatic Target Recognition on Splash 2,” Proceedings of IEEE Symposium on FPGAs for Custom Computing Machines, J.M. Arnold and K.L. Pocek (Eds.), Napa, CA, Apr. 1997.

SUIF Group. Suif Compiler System. http://suif.stanford.edu, 1997.

M. Gokhale and J.M. Stone, “Automatic Allocation of Arrays to Memories in FPGA Processors with Multiple Memory Banks,” Proceedings of IEEE Symposium on FPGAs for Custom Computing Machines, J.M. Arnold and K.L. Pocek (Eds.), Napa, CA, Apr. 1999.

M. Gokhale and J. Stone, “Napa C: Compiling for a Hybrid Risc/FPGA Architecture,” IEEE Symposium on FPGAs for Custom Computing Machines, K. Pocek and J. Arnold (Eds.), Napa Valley, CA, Apr. 1998, pp. 126–135.

M. Gokhale and E. Gomersall, “High Level Compilation for Fine Grained FPGAS,” Proceedings of IEEE Symposium on FPGAs for Custom Computing Machines, J.M. Arnold and K.L. Pocek (Eds.), Napa, CA, Apr. 1997.

E. Waingold, M. Taylor, P. Srikrishna, V. Sarkar, W. Lee, V. Lee, J. Kim, M. Frank, P. Finch, R. Barua, J. Babb, S. Amarasinghe, and A. Agarwal, “Baring it All to Software: Raw Machines,” IEEE Computer, 1997, pp. 86–93.

T. Callahan and J. Wawrzynek, “Instruction Level Parallelism for Reconfigurable Computing,” Proceedings of FPL' 98, Field-Programmable Logic and Applications, 8th International Workshop, Estonia, Sept. 1998. Published in Springer-Verlag Lecture Notes in Computer, Hartenstein and Keevallik (Eds.).

R. Harr, Nimble Compiler. http://www.arpa.mil/ito/psum1998/, 1998.

I. Page, “Construction of Hardware-Software Systems from a Single Description,” Jounal of VLSI Signal Processing, vol. 12, 1996, pp. 87–107.

M. Weinhardt, “Portable Pipeline Synthesis for FCCMS,” Technical Report, Universitat Karlsruhe, 1996.

M. Weinhardt and W. Luk, “Pipeline Vectorization for Reconfigurable Systems,” Proceedings of IEEE Symposium on FPGAs for Custom Computing Machines, J.M. Arnold and K.L. Pocek (Eds.), Napa, CA, Apr. 1999.

T. Garverick, C. Rupp, and J. Arnold, Napa 1000. http://www.national.com/appinfo/milaero/napa1000/, 1997.

High Performance Fortran. Hpf Forum. http://www.crpc.rice.edu/HPFF/home.html, 1999.

M. Lam, “Software Pipelining: An Effective Scheduling Technique for VLIW Machines,” SIG-PLAN' 88, June 1988.

C.R. Rupp, D4 Language Reference Guide and Specification, 1996.

C.R. Rupp, D4 User's Guide, 1996.

D. Green, Modern Logic Design, Addison-Wesley, 1986.

M. Gokhale, Compiling for FPGA-Based Parallel Processors. http://www.sarnoff.com:8000/acshome/fpgahome.html, 1997.

M. Martinosi, Performance and Synthesis Tools for Adaptive Computing. //http://www.ee.princeton.edu/mrm/resconf.html, 1997.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Gokhale, M.B., Stone, J.M. & Gomersall, E. Co-Synthesis to a Hybrid RISC/FPGA Architecture. The Journal of VLSI Signal Processing-Systems for Signal, Image, and Video Technology 24, 165–180 (2000). https://doi.org/10.1023/A:1008141305507

Published:

Issue Date:

DOI: https://doi.org/10.1023/A:1008141305507