Abstract

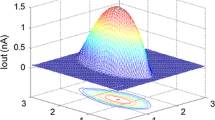

Unique designs for CMOS analog arithmetic circuits are presented which perform addition (V1 + V2), subtraction (V2 − V1), add/invert −(V1 + V2), and multiply (V1 × V2). The circuit operation is based on the inherent square law of MOS transistor drain current when operating in the saturation region. Key features include: good linearity and accuracy, single ended voltage inputs and output, wide input and output range and no input bias voltages. The circuits can be directly coupled (no buffer) and serve as basic building blocks for analog signal processing implementations such as analog filters and adaptive equalizers. All circuits were implemented in 1.2 μm CMOS technology.

Similar content being viewed by others

References

Christian Lutkemyes and Tobias Noll, "A transversal equalizer with an increased adoptive speed avid capability," IEEE Journal of Solid State Circuits, Vol. 33, No. 3, pp. 503–507, 1998.

Xiaodong Wang and Richard Spenser, "A low-power 170 MHz discrete time analog FIR filter," IEEE Journal of Solid State Circuits, Vol. 33, No. 3, pp. 417–426, 1998.

Gabriel Gomez and Raymond Siferd, "An adaptive noise canceller implemented with CMOS analog technology," Journal of Circuits Systems and Computers, Vol. 6, No. 2, pp. 139–154, 1996.

David A. Martin, Hae-Seung Lee, and Ichiro Masaki, "A mixedsignal array processor with early vision applications," IEEE Journal of Solid State Circuits, Vol. 33, No. 3, pp. 497–502, 1998.

Shuo-Yuan Hsiao and Chung-Yu Wu, "A parallel structure for CMOS four quadrant analog multipliers and its application to a 2 GHz RF downconversion mixer," IEEE Journal of Solid State Circuits, Vol. 33, No. 6, pp. 859–869, 1998.

Gian Marco Bo, Daniel D. Caviglia, and Maurizio Valle, "An analog VLSI implementation of a feature extractor for real-time optical character recognition," IEEE Journal of Solid State Circuits, Vol. 33, No. 4, pp. 556–564, 1998.

David A. Johns and Ken Martin, Analog Integrated Circuit Design, John Wiley and Sons, 1997.

Ho-Jun Song and Choong-Kikim, "An MOS four-quadrant analog multiplier using simple two input squaring circuits with a source follower," IEEE Journal of Solid State Circuits, Vol. 25, No. 3, pp. 841–848, 1990.

Raymond E. Siferd, "A GaAs four quadrant analog multiplier circuit," IEEE Journal of Solid State Circuits, Vol. 28, No. 3, 1993.

Seyed R. Zarabadi, Mohammed Ismail, and Chung-Chih Hung, "High performance analog VLSI computational circuits," IEEE Journal of Solid State Circuits, Vol. 33, No. 4, pp. 644–649, 1998.

R. Jacob Baker, Harry W. Li, and David E. Boyce, "CMOS Circuit Design, Layout, and Simulation," The Institute of Electrical and Electronics Engineers, 1998.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Xu, J., Siferd, R. & Ewing, R.L. High Performance CMOS Analog Arithmetic Circuits. The Journal of VLSI Signal Processing-Systems for Signal, Image, and Video Technology 22, 103–111 (1999). https://doi.org/10.1023/A:1008143206419

Published:

Issue Date:

DOI: https://doi.org/10.1023/A:1008143206419