Abstract

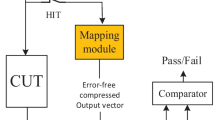

This paper presents a High-Level EDA environment based on the Hierarchical Distributed BIST (HD-BIST), a flexible and reusable approach to solve BIST scheduling issues in System-on-Chip applications. HD-BIST allows activating and controlling different BISTed blocks at different levels of hierarchy, with a minimum overhead in terms of area and test time. Besides the hardware layer, the authors present the HD-BIST application layer, where a simple modeling language, and a prototypical EDA tool demonstrate the effectiveness of the automation of the HD-BIST insertion in the test strategy definition of a complex System-on-Chip.

Similar content being viewed by others

References

F. Beenker, R. Dekker, and R. Stans, “Implementing MACRO Test in Silicon Compiler Design,” IEEE Design & Test of Computers, Vol. 7(2), pp. 41-51, April 1990.

O.F. Haberl and T. Kropf, “HIST, A Methodology for the Automatic Insertion of a Hierarchical Self Test,” Proc. IEEE Int. Test Conference, 1992, pp. 732-741.

Y. Zorian, “A Distributed BIST Control Scheme for Complex VLSI Devices,” Proc. IEEE VLSI Test Symposium, April 1993, pp. 4-9.

A. Benso, S. Chiusano, P. Prinetto, and Y. Zorian, “HD-BIST: A Hierarchical Framework for BIST Scheduling and Diagnosis in SoCs,” Proc. IEEE Int. Test Conference, September 1999, pp. 993-1000.

http://grouper.ieee.org/groups/1500

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Benso, A., Cataldo, S., Chiusano, S. et al. A High-Level EDA Environment for the Automatic Insertion of HD-BIST Structures. Journal of Electronic Testing 16, 179–184 (2000). https://doi.org/10.1023/A:1008326928340

Issue Date:

DOI: https://doi.org/10.1023/A:1008326928340