Abstract

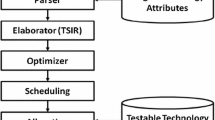

In this study, we present a high-level testability analysis technique that evaluates the testability of a design based on the proposed controllability and observability measures. The control-data flow graph (CDFG) constructed from the VHDL description of a design is first analyzed to identify hard-to-control conditional branches and hard-to-control/observe register transfer statements. After the hard-to-test areas of the design are identified, the proposed testability enhancement methods can be applied to improve the testability of the circuit. Unlike many recent studies in the area of high-level test synthesis (HLTS) that focus on improving the testability of data paths, our approach also improves the testability of synthesized circuits by enhancing the controllability of the control flow. Experimental results on several high-level synthesis benchmarks show that when this approach is used prior to logic synthesis, the test generation complexities are reduced while better fault coverage and ATPG efficiency are often achieved. Implementation of this technique requires minimal logic and performance overheads and allows test vectors to be applied at clock-speed.

Similar content being viewed by others

References

C.A. Papachristou and J.E. Carletta, “Test Synthesis in the Behavioral Domain,” Proc. Int. Test Conf., 1995, pp. 693–702.

J.E. Carletta and C.A. Papachristou, “Testability Analysis and Insertion for RTL Circuits Based on Pseudorandom BIST,” Proc. IEEE Int. Conf. Computer Design, 1995, pp. 163–167.

S. Chiu and C.A. Papachristou, “A Design for Testability Scheme with Applications to Data Path Synthesis,” Proc. IEEE Design Automation Conf., 1991, pp. 271–277.

M.L. Flottes, R. Pires, and B. Rouzeyre, “Analyzing Testability from Behavioral to RT Level,” Proc. Euro. Design and Test Conf., 1997, pp. 158–165.

M. Potkonjak, S. Dey, and R.K. Roy, “Behavioral Synthesis of Area-Efficient Testable Designs using Interaction between Hardware Sharing and Partial Scan,” IEEE Trans. Computer-Aided Design, Vol. 14, No.9, pp. 1141–1154, Sept. 1995.

S. Dey and M. Potkonjak, “Nonscan Design-For-Testability Techniques using RT-Level Design Information,” IEEE Trans. Computer-Aided Design, Vol. 16, No. 12, pp. 1488–1506, Dec. 1997.

I. Ghosh, A. Raghunathan, and N.K. Jha, “Design for Hierarchical Testability of RTL Circuits Obtained by Behavioral Synthesis,” Proc. IEEE Int. Conf. Computer Design, 1995, pp. 173–179.

T. Lee, N.K. Jha, and W.H. Wolf “Behavioral Synthesis of Highly Testable Data Paths under the Non-Scan and Partial Scan Environments,” Proc. IEEE Design Automation Conf., 1993, pp. 292–297.

X. Gu, E. Larson, K. Kuchinski, and Z. Peng, “A Controller Testability Analysis and Enhancement Technique,” Proc. Euro. Design and Test Conf., 1997, pp. 153–157.

F.F. Hsu, E.M. Rudnick, and J.H. Patel, “Enhancing High-Level Control-Flow for Improved Testability,” Proc. Int. Conf. Computer-Aided Design, 1996, pp. 322–328.

F.F. Hsu, E.M. Rudnick, and J.H. Patel, “Testability Insertion in Behavioral Descriptions,” Proc. Int. Symp. System Synthesis, 1996, pp. 139–144.

C. Chen and D.G. Saab, “A Novel Behavioral Testability Measure,” IEEE Trans. Computer-Aided Design, Vol. 12, No. 12, pp. 1960–1970, Dec. 1993.

C. Chen, T. Karnik, and D.G. Saab, “Structural and Behavioral Synthesis for Testability Techniques,” IEEE Trans. Computer-Aided Design, Vol. 13, No. 6, pp. 777–785, June 1994.

X. Gu, K. Kuchinski, and Z. Peng, “Testability Analysis and Improvement from VHDL Behavioral Specifications,” Proc. Euro. Design Automation Conf., 1994, pp. 644–649.

P. Vishakantaiah and J.A. Abraham, “High-Level Testability Analysis using VHDL Descriptions,” Proc. Euro. Conf. Design Automation (EDAC), 1993, pp. 170–174.

P. Vishakantaiah, T. Thomas, J.A. Abraham, and M.S. Abadir, “AMBIANT: Automatic Generation of Behavioral Modifications for Testability,” Proc. IEEE Int. Conf. Computer Design, 1993, pp. 63–66.

X. Gu, K. Kuchinski, and Z. Peng, “An Efficient and Economic Partitioning Approach for Testability,” Proc. Int. Test Conf., 1995, pp. 403–412.

M. Potkonjak, S. Dey, and R.K. Roy, “Considering Testability at Behavioral Level: Use of Transformations for Partial Scan Cost Minimization under Timing and Area Constraints,” IEEE Trans. Computer-Aided Design, Vol. 14, No. 5, pp. 531–546, May 1995.

S. Dey and M. Potkonjak, “Transforming Behavioral Specifications to Facilitate Synthesis of Testable Designs,” Proc. Int. Test Conf., 1994, pp. 184–193.

S. Dey, M. Potkonjak, and R.K. Roy, “Exploiting Hardware Sharing in High-Level Synthesis for Partial Scan Optimization,” Proc. Int. Conf. Computer-Aided Design, 1993, pp. 20–25.

S. Bhatia and N.K. Jha, “Genesis: A Behavioral Synthesis System for Hierarchical Testability,” Proc. Euro. Design and Test Conf., 1994, pp. 272–276.

T. Lee, N.K. Jha, and W.H. Wolf “Behavioral Synthesis for Easy Testability in Data Path Scheduling,” Proc. Int. Conf. Computer-Aided Design, 1993, pp. 616–619.

B. Rouzeyre, D. Dupont, and G. Sagnes, “Component Selection, Scheduling and Control Scheme for High Level Synthesis,” Proc. Euro. Design and Test Conf., 1994, pp. 482–489.

M.L. Flottes, D. Hammand, and B. Rouzeyre, “High-Level Synthesis for Easy Testability,” Proc. Euro. Design and Test Conf., 1995, pp. 198–206.

I. Ghosh, A. Raghunathan, and N.K. Jha, “A Design for Testability Technique for RTL Circuits using Control-Data Flow Extraction,” Proc. Int. Conf. Computer-Aided Design, 1996, pp. 329–336.

Synopsys Reference Manual: Design Analyzer, Version 1997.01, Nov. 1996.

Sunrise Tests System Reference Manual: Testgen, Version 2.3b, Feb. 1997.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Hsu, F.F., Patel, J.H. High-Level Controllability and Observability Analysis for Test Synthesis. Journal of Electronic Testing 13, 93–103 (1998). https://doi.org/10.1023/A:1008349603232

Issue Date:

DOI: https://doi.org/10.1023/A:1008349603232