Abstract

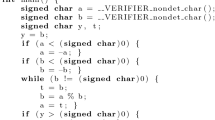

We propose a simulation approach that can take a large design and swiftly cover its valid code-level operating states. The approach perturbs the program-control flow during the simulation to dynamically exhaust all branching possibilities in a verification code/program. The heuristic uses the program branching information from preprocessing the test/verification code. Using the branching information the simulation allows automatic run-time forced branching to make possible a full coverage of the instruction space spanned by the verification code/program. The aim is (1) to improve the verification simulation speed and (2) to get higher coverage rate for large core-base designs such as microprocessors or digital-signal-processing (DSP) products. A case study of a 32-bit RISC processor, used in a network system, is conducted. The application code for the processor (MCP, Myrinet control program) is used as a verification program. Despite the deviation from the valid “software-reachable state” of the system due to forced branching, a significant number of hard-to-reach hardware states (that can be reached only through the right mix of codes, often the code segments of an application software) are covered. Using the MCP program over 30% additional coverage is achieved with the proposed approach over ordinary code-based simulation for a fixed verification time. Further, compared to the conventional simulation approach, the proposed heuristic takes about 43% less compute-cycles to achieve same state coverage level.

Similar content being viewed by others

References

J.W. Duran and S.C. Ntafos, “An Evaluation of Random Testing, ” IEEE Transactions on Software Engineering, Vol. SE-10, pp. 438–444, July 1984.

Li-C. Wang and M. Ray Mercer, “A Better ATPG Algorithm and Its Design Principles, ” ICCD, 1996, pp. 248–252.

D. Brand, “Exhaustive Simulation Need Not Require an Exponential Number of Tests, ” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 12, No. 11, pp. 1635–1641, Nov. 1993.

G. Rothermel and M.J. Harrold, “Analyzing Regression Test Selection Techniques, ” IEEE Transactions on Software Engineering, Vol. 22, No. 8, pp. 529–551, Aug. 1996.

A. Evans, A. Silburt, G. Vrckovnik, T. Brown, M. Dufresne, G. Hall, Tung Ho, and Ying Liu, “Functional Verification of Large ASICs, ” Design Automation Conference, 1998, ACM, pp. 650–655.

R. Vemuri and R. Kalyanaraman, “Generation of Design Verification Tests from Behavioral VHDL Programs Using Path Enumeration and Constraint Programming, ” IEEE Trans on VLSI Systems, Vol. 3, No. 2, pp. 201–214, June 1995.

J.R. Wallack and R. Dandapani, “Coverage Metrics for Functional Tests, ” VLSI Test Symposium, 1994, pp. 176–181.

F. Fallah, S. Devadas, and K. Keutzer, “OCCOM: Efficient Computation of Obervability-Based Code Coverage Metrics for Functional Verification, ” DAC, pp. 152–157, 1998.

R.C. Ho, C. Han Yang, M.A. Horowitz, and D.L. Dill, “Architecture Validation for Processors, ” Proceedings of the 22nd Annual International Symposium on Computer Architecture, Santa Margherita Ligure, Italy, June 22–24, 1995, ACM SIGARCH and IEEE Computer Society TCCA, pp. 404–413.

D. Geist, M. Farkas, A. Landver, Y. Lichtenstein, S. Ur, and Y. Wolfsthal, “Coverage-Directed Test Generation Using Symbolic Techniques, ” Proc. of Int. Conf. on Formal Method in CAD, Nov. 1996.

The VIS Group, “VIS: Verification Interacting with Synthesis, ” URL: http://www-cad.eecs.berkeley.edu/Respep/ Research/vis.

G.S. Choi and K.J. Lee, “A Simulation Environment for Fault-Tolerant Evaluation, ” Technical Report, Texas A&M University, 1996.

Myricom, “LANai 3.0, ” URL: http://www.myri.com:80/ scs/L3.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Min, B., Choi, G. Verification Simulation Acceleration Using Code-Perturbation. Journal of Electronic Testing 16, 83–90 (2000). https://doi.org/10.1023/A:1008396907842

Issue Date:

DOI: https://doi.org/10.1023/A:1008396907842