Abstract

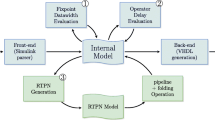

This paper approaches the problem of synthesising an asynchronous control circuit for a stage of the Sproull Counterflow pipeline processor (CFPP) as an exercise in exploiting formal techniques available for Petri nets. We first synthesise a Petri net model of the CFPP stage control from its original “five-state-five-event” description due to Charles Molnar. Secondly, we implement that model in asynchronous circuits, using two-phase and four-phase components. The latter stage involves synthesising circuits with arbitration elements from behavioural descriptions with internal conflicts. This exercise appears to be quite instructive in the sense that it helps to estimate the scope and power of formal methods and today's automatic tools in assisting the process of asynchronous design.

Similar content being viewed by others

References

K. van Berkel, J. Kessels, M. Roncken, R. Saejis and F. Schalij, “The VLSI-programming language Tangram and its translation into handshake circuits,” in Proc. EDAC'91, 1991, pp. 384–389.

L. Bernardinello, G. De Michelis, K. Petruni and S. Vigna, “On Synchronic Structure of Transition Systems,” Universita di Milano, 1994.

R.K. Brayton, G.D. Hachtel, C.T. McMullen, A. Sangiovanni-Vincentelli, Logic Minimisation Algorithms for VLSI Synthesis, Kluwer Academic Publishers, Hingham, MA, 1984.

J. Cortadella, M. Kishinevsky, L. Lavagno and A. Yakovlev, “Synthesizing Petri Nets from State-Based Models,” Technical Report RR 95/09 UPC/DAC, Universitat Politecnica de Catalunya, April 1995.

J. Cortadella, M. Kishinevsky, L. Lavagno and A. Yakovlev, “Synthesizing Petri nets from state-based models,” pp. 164–171, November 1995.

J. Cortadella, A. Kondratyev, M. Kishinevsky, L. Lavagno and A. Yakovlev, “Complete state encoding based on theory of regions,” Proc. Sec. Int. Symp. on Advanced Research in Asynchronous Circuits and Systems, Aizu, Japan, IEEE Comp. Soc. Press, March 1996, pp. 36–47.

J. Cortadella, A. Kondratyev, M. Kishinevsky, L. Lavagno and A. Yakovlev, “Methodology and tools for complete state coding in STG-based synthesis of asynchronous circuits,” in Proc. DAC'96, Las Vegas, June 1996, pp. 63–66.

J. Cortadella, A. Kondratyev, M. Kishinevsky, L. Lavagno and A. Yakovlev. “Petrify: a tool for manipulating concurrent specifications and synthesis of asynchronous controllers,” Proc. Eleventh Conf. Design of Integrated Circuits and Systems (DCIS'96), Barcelona, November 1996, pp. 205–210.

J. Cortadella, L. Lavagno, P. Vanbekbergen and A. Yakovlev, “Designing asynchronous circuits from behavioural specifications with internal conflicts,” Proceedings of First Int. Symp. on Adv. Res. in Asynch. Circ. and Syst., Salt Lake City, Utah, IEEE Comp. Soc. Press, November 1994, pp. 106–115.

_P. Day and J.V. Woods, “Investigation into micropipeline latch design styles,” IEEE Transactions on VLSI Systems, 3:264–272, June 1995.

S. Furber and P. Day, “Four-Phase Micropipeline Latch Control Circuits,” IEEE Transactions on VLSI Systems, 4:247–253, June 1996.

S. Furber, P. Day, J.D. Garside, N.C. Paver and J.V. Woods, “AMULET1: A micropipelines ARM,” Proceedings of VLSI'93, Grenoble, France, September 1993, Best Paper Award.

H. Hulgaard and S.M. Burns, “Bounded delay timing analysis of a class of CSP programs with choice”, Proceedings of Int. Conf. on Adv. Res. in Asynch. Circ. and Syst., Salt Lake City, Utah, November 1994, pp. 2–11.

M. Kishinevsky, A. Kondratyev, A. Taubin and V. Varshavsky, Concurrent Hardware: The Theory and Practice of Self-Timed Design, John Wiley and Sons, London, 1993.

W.H.F.J. Körver and I.M. Nedelchev, “An Asynchronous Implementation of SCPP-A,” Technical Report CSRG95-07, University of Surrey, Guildford, July 1995.

P.G. Lucassen and J.T. Udding, “On the Correctness of the Sproull Counterflow Pipeline Processor,” in Proceedings of the Sec. Int. Symp. on Adv. Res. in Asynch. Circ. and Syst., Aizu-Wakamatsu, Japan, IEEE Comp. Soc. Press, March 1996, pp. 112–120.

R. Milner, Communication and Concurrency, Prentics Hall International, Series in Computer Science, London, 1989.

C.E. Molnar and H.M. Schols, “The Design Problem SCPP-A,” Technical Report TR-95-49, Sun Microsystems Laboratories, Mountain View, CA, December 1995.

T. Murata, “Petri Nets: Properties, Analysis and Applications,” Proceedings of the IEEE, April 1989, pp. 541–580.

C.J. Myers and T.H.-Y. Meng, “Synthesis of timed asynchronous circuits,” IEEE Transactions on VLSI Systems, 1: 106–119, June 1993.

M. Nielsen, G. Rozenberg and P.S. Thiagarajan, “Elementary transition systems,” Theoretical Computer Science, 96:3–33, 1992.

S.S. Patil, “Cellular Arrays for Asynchronous Control,” in Proc. 7th Annual Workshop on Microprogramming, 1974 (also Computation Structures Group Memo. 122, Project MAC, MIT, April 1975).

S.S. Patil and J.B. Dennis, “The description and realization of digital systems,” in Proceedings of the IEEE COMPCOM, 1972, pp. 223–226.

P. Patra and D.S. Fussell, “Efficient building blocks for delay insensitive circuits,” in Proceedings of First Int. Symp. on Adv. Res. in Asynch. Circ. and Syst., Salt Lake City, Utah, IEEE Comp. Soc. Press, pp. 196–205, November 1994.

M. Pietkiewicz-Koutny and A. Yakovlev, “Non-pure nets and their transition systems,” Technical Report Series, no. 528, Department of Computing Science, University of Newcastle upon Tyne, September 1995.

T.G. Rokicki, “Representing and Modeling Digital Circuits,” Ph.D. thesis, Stanford University, 1993.

A. Semenov and A. Yakovlev, “Combining partial orders and symbolic traversal for efficient verification of asynchronous circuits,” Proc. IFIP Int. Conference on Computer Hardware Description Languages, (CHDL'95), Chiba, Japan, August-September 1995, pp. 567–573.

A. Semenov and A. Yakovlev. “Verification of asynchronous circuits based on timed Petri net unfolding,” Proc. 33rd Design Automation Conference DAC'96, Las Vegas, June 1996, pp. 59–63.

E. M. Sentovich, K. J. Singh, L. Lavagno, C. Moon, R. Murgai, A. Saldanha, H. Savoj, P. R. Stephan, R. K. Brayton and A. Sangiovanni-Vincentelli, “SIS: A System for Sequential Circuit Synthesis,” University of California at Berkeley, UCB/ERL M92/41, May 1992.

R.F. Sproull, I. Sutherland and C.E. Molnar, “The Counterflow Pipeline Processor Architecture,” IEEE Design and Test of Computers, Fall 1994, pp. 48–59.

I. E. Sutherland, “Micropipelines,” Communications of the ACM, 32:720–738, Turing Award Lecture, June 1989.

V. I. Varshavsky, M. A. Kishinevsky, V. B. Marakhovsky, V. A. Peschansky, L. Y. Rosenblum, A. R. Taubin and B. S. Tzirlin, Self-timed Control of Concurrent Processes, Kluwer Academic Publishers, Boston/Dordrecht/London, 1990, (Russian edition: 1986).

A. Yakovlev, “Designing Control Logic for Counterflow Pipeline Processor Using Petri nets,” Technical Report no. 522, Department of Computing Science, University of Newcastle upon Tyne, May 1995.

A. Yakovlev, A.M. Koelmans and L. Lavagno, “High level modelling and design of asynchronous interface logic,” IEEE Design and Test of Computers, Spring 1995, pp. 32–40.

A. Yakovlev, A. Koelmans and L. Lavagno. “High Level Modelling and Design of Asynchronous Interface Logic,” Technical Report Series, no. 460, University of Newcastle upon Tyne, Department of Computing Science, November 1993.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Yakovlev, A. Designing Control Logic for Counterflow Pipeline Processor Using Petri Nets. Formal Methods in System Design 12, 39–71 (1998). https://doi.org/10.1023/A:1008649930696

Issue Date:

DOI: https://doi.org/10.1023/A:1008649930696