Abstract

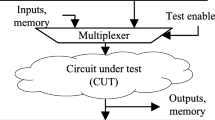

The combination of higher quality requirements and sensitivity of high performance circuits to delay defects has led to an increasing emphasis on delay testing of VLSI circuits. As delay testing using external testers requires expensive ATE, built-in self test (BIST) is an alternative technique that can significantly reduce the test cost.

It has been proven that Single Input Change (SIC) test sequences are more effective than classical Multiple Input Change (MIC) test sequences when a high robust delay fault coverage is targeted. It has also been shown that random SIC (RSIC) test sequences achieve a higher fault coverage than random MIC (RMIC) test sequences when both robust and non robust tests are under consideration; the experimental results were based on a software generation of RSIC sequences that are easily generated.

Obviously, a hardware RSIC generation providing similar results can be obtained. However, this hardware generator must be carefully designed. In this paper, it is explained what are the criteria which must be satisfied for this purpose. A solution is proposed and illustrated with an example. Then, it is shown that a bad result may be obtained if one of these criteria is not satisfied.

Similar content being viewed by others

References

M. Abramovici, M.A. Breuer, and A.D. Friedman, Digital Systems Testing and Testable Design, New York: Comp. Sc. Press, 1990.

P.H. Bardell and W.H. McAnney, “Pseudorandom Arrays for Built-In Tests,” IEEE Trans. on Comp., vol. 35, no. 7, pp. 653–658, 1986.

F. Brglez, D. Bryant, and K. Kozminski, “Combinational Pro-files of Sequential Benchmark Circuits,” in IEEE Int. Symp. on Circuits and Systems, 1989, pp. 1929–1934.

S. Crépaux-Motte, M. Jacomino, and R. David, “An Algebraic Method for Delay Fault Testing,” in IEEE VLSI Test Symposium, 1996, pp. 308–315.

R. David, Random Testing of Digital Circuits: Theory and Applications, New York: Marcel Dekker, 1998.

P. Girard, C. Landrault, V. Moréda, and S. Pravossoudovitch, “An Optimized BIST Test Pattern Generator for Delay Testing,” in IEEE VLSI Test Symposium, 1997, pp. 94–99.

D.E. Knuth, The Art of Computer Programming, vol. 2: Seminumerical Algorithms, Reading, MA: Addison-Wesley, 1969.

J. Rajski, G. Mrugalski, and J. Tyszer, “Comparative Study of CA-based PRPGs and LFRSs with Phase Shifters,” in IEEE VLSI Test Symposium, 1999, pp. 236–245.

G.L. Smith, “Model for Delay Faults Based upon Paths,” in Int. Test Conference, 1985, pp. 342–349.

TestGen, version Tg4.1 User Guide, Synopsys Inc., 1999.

A. Virazel, “Test Inté,gré des Circuits Digitaux: Analyse et Génération de Séquences Aléeatoires Adjacentes,” Ph.D. thesis, Univ. of Montpellier, November 2001.

A. Virazel, R. David, P. Girard, C. Landrault, and S. Pravossoudovitch, “Delay Fault Testing: Effectiveness of Random SIC and Random MIC Test Sequences,” Journal of Electronic Testing, vol. 17, no. 3/4, pp. 233–241, 2001.

W. Wang and S.K. Gupta, “Weighted Random Robust Path Delay Testing of Synthesized Multilevel Circuits,” in IEEE VLSI Test Symposium, 1994, pp. 291–297.

H.J. Wunderlich and Y. Zorian, Built-In Self Test (BIST): Synthesis of Self-Testable Systems, Boston, MA: Kluwer Acad. Pub., 1997.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

David, R., Girard, P., Landrault, C. et al. Hardware Generation of Random Single Input Change Test Sequences. Journal of Electronic Testing 18, 145–157 (2002). https://doi.org/10.1023/A:1014941525735

Issue Date:

DOI: https://doi.org/10.1023/A:1014941525735