Abstract

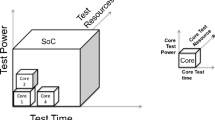

In this paper, a method to solve the resource allocation and test scheduling problems together in order to achieve concurrent test for core-based System-On-Chip (SOC) designs is presented. The primary objective for concurrent SOC test is to reduce test application time under the constraints of SOC pins and peak power consumption. The methodology used in this paper is not limited to any specific Test Access Mechanism (TAM). Additionally, it can also be applied to SOC budgeting at design phase to predict a tradeoff between test application time and SOC pins needed. The contribution of this paper is the formulation of the problem as a well-known 2-dimensional bin-packing problem. A best-fit heuristic algorithm is adopted to achieve optimal solution.

Similar content being viewed by others

References

D. Bagchi, D.R. Chowdhury, and J. Mukherjee, “A Novel Strategy to Test Core Based Designs, ” in VLSI Design 2001. pp. 122–127.

K. Chakrabarty, “Test Scheduling for Core-Based Systems Using Mixed-Integer Linear Programming, ” in IEEE TCAD, vol. 19, pp. 1163–1174, Oct. 2000.

K. Chakrabarty, “Design of System-on-a-Chip Test Access Architectures Using Integer Linear Programming, ” in VTS 2000. pp. 127–134.

K. Chakrabarty, “Design of System-on-a-Chip Test Access Architectures Under Place-and-Route and Power Constraints, ” in DAC 2000. pp. 432–437.

E.G. Coffman, M.R. Garey, D.S. Johnson, and R.E. Tarjan, “Performance Bounds for Level-Oriented Two-Dimensional Packing Algorithms, ” SIAM J. Computer, pp. 808–826, 1980.

R. Fenrich, R. Miller, and Q.F. Stout, “Multi-Tiered Algorithms for 2-Dimensional Bin Packing, ” in Proc. of Distributed Memory Computing Conference, 1990.

I. Ghosh, S. Dey, and N.K. Jha, “A Fast and Low-Cost Testing Technique for Core-Based System-Chips, ” IEEE TCAD, vol. 19, pp. 863–877, Aug. 2000.

I. Ghosh, N.K. Jha, and S. Dey, “A Low Overhead Design for Testability and Test Generation Technique for Core-Based System-on-a-Chip, ” IEEE TCAD, vol. 18, pp. 1661–1676, Nov. 1999.

V. Immaneni and S. Raman, “Direct Access Test Scheme-Design of Block and Core Cells for Embedded ASICs, ” in ITC 1990. pp. 488–492.

E.J. Marinissen and J. Aerts, “Test Protocol Scheduling for Embedded Core-Based System ICs, ” in IEEE International Workshop of Testing Embedded Core-based System-Chips, 1998.

E.J. Marinissen, R. Arendsen, G. Bos, H. Dingemanse, M. Lousberg, and C. Wouters, “A Structured and Scalable Mechanism for Test Access to Embedded Reusable Cores, ” in ITC 1998. pp. 284–292.

J. Monzel, “Low Cost Testing of System-On-Chip, ” in Proc. Digest of 1st IEEE Internation TECS, 1997.

M. Nourani and C. Papachristou, “An ILP Formulation to Optimize Test Access Mechanism in System-on-Chip Testing, ” in ITC 2000, pp. 902–910.

C.P. Ravikumar, G. Chandra, and A. Verma, “Simultaneous Module Selection and Scheduling for Power-Constrained Testing of Core Based Systems, ” in VLSI Design 2000.

C.P. Ravikumar, A. Verma, and G. Chandra, “A Polynomial-Time Algorithm for Power Constrained Testing of Core Based Systems, ” in ATS 1999, pp. 107–112.

Semiconductor Industry Association, The National Technology Roadmap for Semiconductors, Sematech, Inc. pp. 24, 1997.

M. Sugihara, H. Date, and H. Yasuura, “A Novel Test Methodology for Core-Based System LSIs and a Testing Time Minimization Problem, ” in ITC 1998, pp. 465–472.

N.A. Touba and B. Pouya, “Testing Embedded Cores Using Partial Isolation Rings, ” in VTS 1997, pp. 10–15.

P. Varma and S. Bhatia, “A Structured Test Re-Use Methodology for Core-Based System Chips, ” in ITC 1998, pp. 294–302.

L. Whetsel, “An IEEE 1149.1 Based Test Access Architecture for ICs with Embedded IP Cores, ” in ITC 1997, pp. 69–78

L. Whetsel, “Addressable Test Ports An Approach to Testing Embedded Cores, ” in ITC 1999, pp. 1055–1064.

Y. Zorian, “Test Requirement for Embedded Core-Based Systems and IEEE P1500, ” in ITC 1997, pp. 191-199.

Y. Zorian, E.J. Marinissen and S. Dey, “Testing Embedded Core-Based System Chips, ” Computer, vol. 32, no. 6, pp. 52–60, June 1999.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Huang, Y., Cheng, WT., Tsai, CC. et al. On Concurrent Test of Core-Based SOC Design. Journal of Electronic Testing 18, 401–414 (2002). https://doi.org/10.1023/A:1016541407006

Issue Date:

DOI: https://doi.org/10.1023/A:1016541407006