Abstract

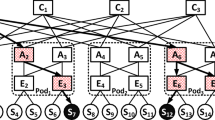

In this paper, we present the design of a large self-routing multicast ATM switch. The switch consists of a sorting network followed by a 3-stage routing network. We first present a simple design of a large sorting network built using small sized shared memory that can be used as a building block for a large sorting network. Small sized shared memory is also used in the 3-stage routing network making the switch modular and easy to implement using current VLSI technology. As the network uses shared memory modules, multicasting functionality is easily built into the network. The performance of the proposed network is compared with an equivalent completely shared memory switch using computer simulations under bursty traffic model. The results show that the proposed network has better performance in terms of cell loss ratio than the completely shared memory switch under moderate to heavy traffic load (0.6 ≤ effective offered load ≤ 1.2). Furthermore, multicast cell delays are drastically improved.

Similar content being viewed by others

References

H. Ahmadi and W.E. Denzel, A survey of modern high-performance switching techniques, IEEE Journal on Selected Areas in Communications 7(7) (1989) 1091–1103.

M. Alimuddin, H. Alnuweiri and R. Donaldson, Efficient design of scalable shared-memory packet switches, in: IEEE Internat. Conf. on Communications (1996) pp. 675–680.

R.Y. Awdeh and H.T. Mouftah, Survey of ATM switch architectures, Computer Networks and ISDN Systems 27 (1995) 1567–1613.

K.E. Batcher, Sorting networks and their applications, in: AFIPS Conference (1968) pp. 307–314.

K. Chan, S. Chan, K. Yeung, K. Ko and E. Wong, Clos-knockout: A large-scale modular multicast ATM switch, in: IEEE GLOBECOM (1996) pp. 1358–1362.

F. Chiussi, Y. Xia and V. Kumar, Performance of shared-memory switches under multicast bursty traffic, in: IEEE GLOBECOM (1995) pp. 1231–1237.

A.K. Chodhury and E.L. Hahne, Buffer management in a hierarchical shared memory switch, in: IEEE INFOCOM (1994) pp. 1410–1419.

N. Endo, T. Kozaki, T. Ohuchi, H. Kuwahara and S. Gohara, Shared buffer memory switch for an ATM exchange, IEEE Transactions on Communications 41(1) (1993) pp. 237–245.

K. Eng, M. Karol and Y. Yeh, A growable packet (ATM) switch architecture: Design principles and applications, IEEE Transactions on Communications 40(2) (1992) 423–430.

K.Y. Eng, M.A. Pashan, R.A. Spanke, M.J. Karol and G.D. Martin, A high-performance prototype 2.5 Gb/s ATM switch for broadband applications, in: IEEE GLOBECOM (1992) pp. 111–117.

J. Garcia-Haro and A. Jayszczyk, ATM shared-memory switching architectures, IEEE Network (July/August 1994) 18–26.

L. Goke and G. Lipsvski, Banyan networks for partitioning multiprocessors, in: 1st Annual Sympos. on Computer Architecture (1973) pp. 21–28.

A. Jajszczyk and W. Kabacinski, A growable shared-buffer-based ATM switching fabric, in: IEEE GLOBECOM (1993) pp. 29–33.

A. Jajszczyk and M. Roszkiewicz, Optimum structures and growability of shared-buffer fabrics, in: IEEE GLOBECOM (1994) pp. 309–313.

T. Kozaki, N. Endo, Y. Sakurai, O. Matsubara, M. Mizukami and K. Asano, 32 x 32 shared buffertype ATM switch VLSIs for BISDNs, IEEE Journal on Selected Areas in Communications 9(8) (1991) 1239–1247.

S. Kumar and D.P. Agrawal, On design of a shared-buffer-based ATM switch for broadband-ISDN, in: IEEE Internat. Phoenix Conf. on Computers Communications (1994) pp. 377–383.

S. Kumar and D.P. Agrawal, A shared-buffer direct-access (SBDA) switch architecture for ATMbased networks, in: IEEE Internat. Conf. on Communications (1994) pp. 101–105.

S. Kumar and D. Agrawal, On multicast support for shared-memory based ATM switch architecture, IEEE Network (January/February 1996) 34–39.

K. Law and A. Leon-Garcia, A growable large scale ATM multicast switch, in: IEEE Internat. Conf. on Communications (1996) pp. 1695–1699.

S. Liew and K. Lu, Comparison of buffering strategies for asymmetric packet switch modules, IEEE Journal on Selected Areas in Communications 9(3) (1991) 428–438.

J. Lin and C. Wu, A novel architecture for an ATM switch, in: IEEE Internat. Conf. on Computer Design (1995) pp. 340–345.

I. Mitrani, Simulation Techniques for Discrete Event Systems (Cambridge Univ. Press, Cambridge, 1992) pp. 86–105.

Y. Oie, T. Suda, M. Murata, D. Kolson and H. Miyahara, Survey of switching techniques in highspeed networks and their performance, in: IEEE INFOCOM (1990) pp. 1242–1251.

A. Pattavina, Nonblocking architectures for ATM switching, IEEE Communications Magazine 31 (1993) 38–48.

R. Rooholamini, V. Cherkassky and M. Garver, Finding the right ATM switch for the market, Computer Magazine (April 1994) 16–28.

N.K. Sharma, Modular design of a large sorting network, in: Internat. Sympos. on Parallel Architectures, Algorithms and Networks (1997).

Y. Sakurai, N. Ido, S. Gohara and N. Endo, Large-scale ATM multistage switching network with shared buffer memory switches, IEEE Communications Magazine (January 1991) 91–96.

N.K. Sharma, Review of recent shared memory based ATM switches, Computer Communications 22(4) (1999) 297–316.

S.X. Wei and V.P. Kumar, On the multiple shared memory module approach to ATM switching, in: IEEE INFOCOM (1992) pp. 116–123.

H. Yamanaka, H. Saito, H. Yamada, M. Tsuzuki, S. Kohama, H. Ueda, H. Kondoh, Y. Matsuda and K. Oshima, 622 Mb/s 8 x 8 shared multibuffer ATM switch with hierarchical queueing and multicast functions, in: IEEE GLOBECOM (1993) pp. 1488–1495.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Sharma, N.K., Ho, J.D. Performance of a large multicast ATM switch. Telecommunication Systems 13, 453–467 (2000). https://doi.org/10.1023/A:1019116728142

Issue Date:

DOI: https://doi.org/10.1023/A:1019116728142