Abstract

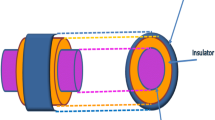

This paper presents a new model for gate-to-channel GOS defects. The transistors used in digital cell library are usually designed with a minimum-size. This new model permits to handle minimal-length transistors allowing the simulation of GOS defects in realistic digital circuits. Based on the electrical analysis of the defect behavior, a comprehensive method for the model construction is detailed. It is shown that the behavior of the proposed model matches in a satisfactory way the behavior of a defective transistor including the random parameters of the defect.

Similar content being viewed by others

References

V. Champac, R. Rodriguez-Montanes, J. Segura, J. Figueras, and J. Rubio, “Fault Modeling of Gate Oxide Short, Floating Gate & Bridging Failures in CMOS Circuits,” in Europ. Test Conf., 1991, pp. 143-148.

H. Hao and E.J. McCluskey, “On the Modeling and Testing of Gate Oxide Shorts in CMOS Logic Gates,” Int. Work. on Defect and Fault Tolerance on VLSI Systems, pp. 161-174, 1991.

H. Hao and E.J. McCluskey, “Analysis of Gate Oxide Shorts in CMOS Circuits,” Trans. on Computers, vol. 42, pp. 1510-1516, 1993.

C.F. Hawkins and J.M. Soden, “Electrical Characteristics and Testing Considerations for Gate Oxide Shorts in CMOS ICs,” in Int. Test Conf., 1985, pp. 544-555.

C.F. Hawkins and J.M. Soden, “Reliability and Electrical Properties of Gate Oxide Shorts in CMOS ICs,” in Int. Test Conf., 1986, pp. 443-451.

M. Renovell, J.M. Gallière, F. Azaïs, and Y. Bertrand, “A Complete Analysis of the Voltage Behaviour of MOS Transistor with Gate Oxide Short,” Defect-Based TestingWork., pp. 5-10, 2001.

M. Renovell, J.M. Gallière, F. Azaïs, and Y. Bertrand, “Analysing the Characteristics of MOS Transistors in the Presence of Gate Oxide Short,” Design & Diag. of Electr. Circuits and Syst., pp. 155-161, 2001.

M. Renovell, J.M. Gallière, F. Azaïs, and Y. Bertrand, “Boolean and Current Detection of MOS Transistor with Gate Oxide Short,” in Int. Test Conf., 2001, pp. 1039-1048.

R. Rodriguez-Montanes, J. Segura, V. Champac, J. Figueras, and J. Rubio, “Current vs. Logic Testing of Gate Oxide Short, Floating Gate and Bridging Failures,” in Int. Test Conf., 1991, pp. 510-519.

J. Segura, C. De Benito, A. Rubio, and C.F. Hawkins, “A Detailed Analysis of GOS Defects in MOS Transistors: Testing Implications at Circuit Level,” in Int. Test Conf., 1995, pp. 544-551.

J. Segura, C. DeBenito, A. Rubio, and C.F. Hawkins, “ADetailed Analysis and Electrical Modeling of Gate Oxide Shorts in MOS Transistors,” JETTA, no. 8, pp. 229-239, 1996.

J. Segura, J. Figueras, and A. Rubio, “Approach to the Analysis of Gate Oxide Shorts in CMOS Digital Circuits,” Microeletron. Reliab., vol. 32, no. 11, pp. 1509-1514, 1992.

J. Segura, A. Rubio, and J. Figueras, “Analysis and Modeling of MOS Devices with Gate Oxide Short Failures,” in Int. Symp. Circuits and Syst., 1991, pp. 2164-2167.

J.M. Soden and C.F. Hawkins, “Test Considerations for Gate Oxide Shorts in CMOS ICs,” Design & Test of Computers, pp. 56-64, 1986.

S.I. Syed and D.M. Wu, “Defect Analysis, Test Generation and Fault Simulation for Gate Oxide Shorts in CMOS ICs,” in Int. Symp. Circuits and Syst., 1990, pp. 2705-2707.

M. Syrzycki, “Modeling of Spot Defects in MOS Transistors,” in Int. Test Conf., 1987, pp. 148-157.

M. Syrzycki, “Modeling of Gate Oxide Shorts in MOS Transistors,” Trans. on Computer-Aided Design, vol. 8, pp. 193-202, 1989.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Renovell, M., Gallière, J., Azaïs, F. et al. Modeling the Random Parameters Effects in a Non-Split Model of Gate Oxide Short. Journal of Electronic Testing 19, 377–386 (2003). https://doi.org/10.1023/A:1024683708105

Issue Date:

DOI: https://doi.org/10.1023/A:1024683708105