Abstract

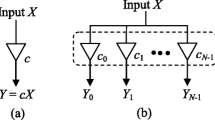

The pipeline form of the serial/parallel multiplier for constant numbers, which operates without insertion of zero words between successive data, is presented. The constant number is in Canonical Signed Digit (CSD) form and the other factor in two's complement form. The CSD form was chosen because it yields significant hardware reduction. Also, for the above data forms the Lyon's serial pipeline multiplier is examined. For these designs, a special algorithm for the multiplication of two's complement numbers with constant numbers in CSD representation was developed. The proposed serial pipeline multipliers are compared with the existing schemes from the point of hardware complexity.

Similar content being viewed by others

References

L. Dadda, “On Serial-Input Multipliers for Two's Complement Numbers,” IEEE Trans. on Comput., vol. 38, no.9, pp. 13411–1345.

R.F. Lyon, “Two's Complement Pipeline Multipliers,” IEEE Trans. Commun., vol. COM-24, no.4, pp. 418–425.

R. Hartley and P. Corbett, “Digit-Serial Processing Techniques,” IEEE Trans. Circuits Syst., vol. CAS-37, 1990, pp. 707–719.

L. Dadda and L. Breveglieri, “A Modular Bit Serial Convolver,” In Wafer Scale Intergration III–Proc. 3rd IFIP, Amsterdam, North Holland 1990, pp. 279–289.

A. Booth, “A Signed Binary Multiplication Technique,” Quart. J. Mech. Appl. Math., vol. 4, 1951, pp. 236–240.

G. Reitwiesner, “Binary Arithmetic,” Advances in Computers, vol. 1, 1996, pp. 231–308.

A. Peled, “On the Hardware Implementation of Digital Signal Processors,” IEEE Trans. Acoust., Speech, Signal Proc., vol. 24, 1976, pp. 76–86.

T. Lin and H. Samueli, “A 200-MHz CMOS x/sin(x) Digital Filter for Compensating D/A Converter Frequency Response Distortion,” IEEE J. of Solid-State Circuits, vol. 26, no.9, 1991, pp. 1278–1285.

S.Y. Kung, “On Supercomputing with Systolic/Wavefront Arrays,” Proc. IEEE, vol. 72, no.7, 1984, pp. 867–884.

C. Caraiscos and K.Z. Pekmestzi, “Low-Latency Bit-Parallel Systolic VLSI Implementation of FIR Digital Filters,” IEEE Trans. Circuits Syst.–II: Analog and Digital Signal Proc., vol. 43, no.7, 1996, pp. 529–534.

K. Pekmestzi and C. Caraiscos, “A Class of Systolic Bit-Serial Multipliers,” Int. J. Electronics, vol. 76, 1994, pp. 463–468.

N. Weste and K. Eshraghian, Principles of CMOS VLSI Design, Reading, MA: Addison-Wesley, 1994.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Pekmestzi, K., Kalivas, P. Constant Number Serial Pipeline Multipliers. The Journal of VLSI Signal Processing-Systems for Signal, Image, and Video Technology 26, 361–368 (2000). https://doi.org/10.1023/A:1026507617721

Published:

Issue Date:

DOI: https://doi.org/10.1023/A:1026507617721