Abstract

Stack filters belong to the class of non-linear filters and include the well-known median filter, weighted median filters, order statistic filters and weighted order statistic filters. Any stack filter can be implemented by using the parallel threshold decomposition architecture which allows implementing their non-linear processing by means of a collection of identical binary filters (Boolean logic circuits). Although it is conceptually simple and useful to study the filter properties, this architecture is not practical for direct hardware implementation because as many as (M − 1) binary filters are required for a M-valued input signal and M is large in many applications.

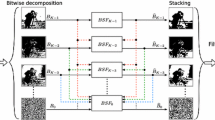

In this paper we introduce a new parallel architecture for stack filter implementations. The complexity is now proportional to the window width L of the filter, instead of to M. In most applications L is much smaller than M which translates into efficient hardware implementations. The attractive characteristic of ease of design exhibited by the threshold decomposition architecture is kept. In fact, for a given stack filter both in the conventional implementation and in the proposed one, the same binary filter is required. The key concept supporting the new architecture is a modified decomposition scheme which generates L binary signals for a multi-valued input. As an application example, a complex WOS filter is designed and prototyped in an FPGA.

Similar content being viewed by others

References

L. Yin, R. Yang, M. Gabbouj, and Y. Neuvo, "Weighted Median Filters: A Tutorial," IEEE Trans.on Circuits and Systems-Part II, vol. 43, no. 3, 1992, pp. 157-192.

W.K. Pratt, Digital Image Procesing, New York: Wiley Interscience, 1978.

B.I. Justusson, "Median Filtering: Statistical Properties," in Topics in Applied Physics, Two-Dimensional Digital Signal Processing II, T.S. Huang (Ed.), Berlin: Springer, 1981.

O. Yli-Harja, J. Astola, and Y. Neuvo, "Analysis of the Properties of Median and Weighted Median Filters Using Threshold Logic and Satck Filter Representation," IEEE Trans.on Signal Processing, vol. 39, no. 2, 1991, pp. 395-409.

P. Wendt, E. Coyle, and N. Gallagher, "Stack Filters," IEEE Trans.on Acoust., Speech, and Signal Process., vol. ASSP-34, 1986, pp. 898-911.

J.P. Fitch, E.J. Coyle, and N.C. Gallagher, "Median Filtering by Threshold Decomposition," IEEE Trans.on Acoust., Speech, and Signal Process., vol. ASSP-32, 1984, pp. 1183-1188.

E.N. Gilbert, "Lattice-theoric Properties of Frontal Switching Functions," Journal Math.Phys., vol. 33, 1954, pp. 57-67.

P. Maragos and R.W. Schafer, "Morphological Filters," IEEE Trans.on Acoust.Speech, and Signal Process., vol. ASSP-35, 1987, pp. 1153-1184.

C. Chakrabarti, "Efficient Stack Filter Implementations of Rank-Order Filters," in Proc.ISCAS'93, 1993, pp. 958-961.

C. Chakrabarti and L.E. Lucke, "VLSI Architectures for Weighted order Statistic (WOS) Filters," in Proc.ISCAS'98, vol. ii, 1998, pp. 320-323.

K. Chen, "Bit-Serial Realization of a Class of Nonlinear Filters Based on Positive Boolean Functions," IEEE Trans.on Acoust.Speech and Signal Process., vol. ASSP-36, no. 6, 1989, pp. 785-794.

D. Gervorkian, K.O. Egiazarian, and S.S. Agaian, "Parallel Algorithms and VLSI Architectures for Stack Filtering Using Fi-bonacci p-Codes," IEEE Trans.on Signal Processing, vol. 43, no. 1, 1995, pp. 286-295.

J. Astola, D. Akopian, O. Vainio, and S. Agaian, "New Digit-Serial Implementations of Stack Filters," Signal Processing, vol. 61, 1997, pp. 181-197.

J.P. Fitch, "Software and VLSI Algorithms for Generalized Ranked order Filtering," IEEE Trans.on Circuits and Systems, vol. CAS-34, no. 5, 1987, pp. 553-559.

G.B. Adams, E.J. Coyle, L. Lin, L.E. Lucke, and K. K. Parhi, "Input Compression and Efficient VLSI Architectures for Rank Order and Stack Filters," Signal Processing, vol. 38, 1994, pp. 441-453.

D. Gecorkian, M. Hu, O. Vainio, and J. Astola, "VLSI Architecture for Stack Filters," in Proc.DSP'97, 1997, pp. 641-644.

M. Hu, O. Vainio, J. Astola, K. Egiazarian, and D. Gecorkian, "RAM-Based Programmable Stack Filter Implementation," in Proc.ISCAS'99, vol. iii, 1999, pp. 474-477.

S. Muroga, Threshold Logic and Its Applications, New York: Wiley Interscience, 1971.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Avedillo, M.J., Quintana, J.M., Alami, H.E. et al. A Practical Parallel Architecture for Stacks Filters. The Journal of VLSI Signal Processing-Systems for Signal, Image, and Video Technology 38, 91–100 (2004). https://doi.org/10.1023/B:VLSI.0000040422.03985.04

Published:

Issue Date:

DOI: https://doi.org/10.1023/B:VLSI.0000040422.03985.04