Abstract

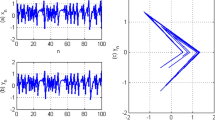

In this paper, energy efficient VLSI architectures for linear turbo equalization are studied. Linear turbo equalizers exhibit dramatic bit error rate (BER) improvement over conventional equalizers by enabling a form of joint equalization and decoding in which soft information is iteratively exchanged between the equalizer and decoder. However, turbo equalizers can be computationally complex and hence require significant power consumption. In this paper, we present an energy-efficient VLSI architecture for such linear turbo equalizers. Key architectural techniques include elimination of redundant operations and early termination. Early termination enables powering down parts of the soft-input soft-output (SISO) equalizer and decoder thereby saving power. Simulation results show that energy savings in the range 30–60% and 10–60% are achieved in equalization and decoding, respectively. Furthermore, we present finite precision requirements of the linear turbo equalizer and an efficient rescaling method to prevent overflow.

Similar content being viewed by others

References

C. Douillard, M. Jezequel, C. Berrou, A. Picart, P. Didier, and A. Glavieux, “Iterative Correction of Intersymbol Interference: Turbo-Equalization,” European Transactions on Telecommunications, vol. 6, 1995, pp. 507–511.

A. Glavieux, C. Laot, and J. Labat, “Turbo Equalization Over a Frequency Selective Channel,” in Symposium on Turbo-Codes, Brest, France, Sept. 1997, pp. 96–102.

C. Laot, A. Glavieux, and J. Labat, “Turbo Equalization: Adaptive Equalization and Channel Decoding Jointly Optimized,” IEEE Journal of Selected Areas in Comm.v,ol. 19, Sept. 2001, pp. 1744–1752.

M. Tüchler, A. Singer, and R. Koetter, “Minimum Mean Squared Error Equalization Using A-Priori Information,” IEEE Trans. on Signal Processing,vol. 50, no. 3, 2002, pp. 673–683.

M. Tüchler, R. Koetter, and A. Singer, “Turbo Equalization: Principles and New Results,” IEEE Trans. on Comm.,vol. 50, no. 5, 2002, pp. 754–767.

J.G. Proakis, Digital Communications, 3rd ed., McGraw-Hill, 1995.

M. Goel and N.R. Shanbhag, “Low-Power Equalizers for 51.84 Mb/s Very High-Speed Digital Subscriber Loop (VDSL) modems,” in Proc. of IEEE Signal Processing Systems(SiPS): Design and Implementation, Oct. 1998, pp. 317–326.

Z. Wang, H. Suzuki, and K.K. Parhi, “VLSI Implementation Issues of Turbo Decoder Design for Wireless Applications,” in Proc. of IEEE Signal Processing Systems(SiPS): Design and Implementation, Oct. 1999, pp. 503–512.

G. Montorsi and S. Benedetto, “Design of Fixed-Point Iterative Decoders for Concatenated Codes with Interleavers,” IEEE Journal on Selected Areas in Comm.,vol. 19, no. 5, May 2001.

J. Hsu and C. Wang, “On Finite-Precision Implementation of a Decoder for Turbo Codes,” in Proc. International Symposium on Circuits and Systems, 1999, vol. 4, pp. 423–426.

P.H. Wu and S.M. Pisuk, “Implementation of a Low Complexity, Low Power, Integer-Based Turbo Decoder,” in Proc. Global Telecommunication Conf., 2001, vol. 2, pp. 946–951.

O. Leung, C. Yue, C. Tsui, and R. Cheng, “Reducing Power Consumption of Turbo Code Decoder Using Adaptive Iteration with Variable Supply Voltage,” in Proc. of IEEE Int. Symp. Low Power Electronics Design (ISLPED'99), San Diego, CA, 1999, pp. 36–41.

D. Garrett, B. Xu, and C. Nicol, “Energy Efficient Turbo Decoding for 3G Mobile,” in Proc. of IEEE Int. Symp. Low Power Electronics Design (ISLPED'01), Huntington Beach, CA, 2001, pp. 328–333.

C. Schurgers, F. Catthoor, and M. Engels, “Memory Optimization of MAP Turbo Decoder Algorithms,” IEEE Trans. on VLSI Systems,vol. 9, no. 2, 2001, pp. 305–312.

M.M. Mansour and N.R. Shanbhag, “VLSI Architectures for SISO-APP Decoders,” IEEE Trans. on VLSI Systems,vol. 11, no. 4, 2003, pp. 627–650.

A.J. Viterbi, “An intuitive Justification and a Simplified Implementation of the MAP Decoder for Convolutional Codes,” IEEE Journal on Selected Areas in Comm.,vol. 16, no. 2, 1998, pp. 260–264.

G. Bauch and V. Franz, “A Comparison of Soft-in/Soft-Out Algorithms for Turbo Detection,” in Proc. of IEEE Int. Conf. on Telecommunications(ICT'98), June 1998, pp. 259–263.

G. Bauch, H. Khorram, and J. Hagenauer, “Iterative Equalization and Decoding in Mobile Communications Systems,” in Proc. of European Personal Mobile Comm. Conf. (EPMCC), Oct. 1997.

G. Bauch, H. Khorram, and J. Hagenauer, “Iterative Equalization and Decoding for the GSMSystem,” in Proc. IEEE Veh. Technol. Conf., Ottawa, vol. 3, May 1998, pp. 2262–2266.

H. Stark and J.W. Woods, Probability, Random Processes, and Estimation Theory for Engineers, 2nd ed., Prentice Hall, 1994.

G.A. Clark, S.K. Mitra, and S.R. Parker, “Block Implementation of Adaptive Digital Filters,” IEEE Transactions on Acoustics, Speech, and Signal Processing, vol. ASSP-29, no. 3, June 1981.

K.K. Parhi, VLSI Digital Signal Processing Systems: Design and Implementation, John Wiley & Sons, Inc., 1999.

J. Hsu and C. Wang, “A Parallel Decoding Scheme For Turbo Codes,” in Proc. IEEE International Symp. on Circuits and Systems, vol. 4, 1998, pp. 445–448.

Z. Wang, Z. Chi, and K. Parhi, “Area-Efficient High Speed Decoding Schemes for Turbo/MAP Decoders,” in Proc. 2001 IEEE International Conference on Acoustics, Speech, and Signal Processing, 2001, vol. 4, pp. 2633–2636.

M.M. Mansour and N.R. Shanbhag, “Design Methodology For High-Speed Iterative Decoder Architectures,” in Proc. 2002 IEEE International Conference on Acoustics, Speech, and Signal Processing,vol. 3, 2002, pp. 3085–3088.

S. ten Brink, “Convergence Behavior of Iteratively Decoded Parallel Concatenated Codes,” IEEE Trans. on Comm., vol. 49, 2001, pp. 1727–1737.

J. Hokfelt, O. Edfors, and T. Maseng, “Interleaver Design for Turbo Codes Based on the Performance of Iterative Decoding,” in Proc. of International Conf. on Comm., 1999, pp. 93–97.

A.P. Hekstra, “An Alternative to Metric Rescaling in Viterbi Decoders,” IEEE Trans on Comm.,vol. 37, no. 11, pp. 1220–1222.

C.B. Shung, P.H. Siegel, G. Ungerboeck, and H.K. Thapar, “VLSI Architecture for Metric Normalization in the Viterbi Algorithm,” in Proceeding of IEEE International Conf. on Comm., 1990, vol. 4, pp. 1723–1728.

A.P. Hekstra, “On the Maximum Difference Between Path Metrics in a Viterbi Decoder,” in Proceeding of IEEE International Symposium on Information Theory, 1993, pp. 21-21.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Lee, SJ., Shanbhag, N.R. & Singer, A.C. Energy Efficient VLSI Architecture for Linear Turbo Equalizer. The Journal of VLSI Signal Processing-Systems for Signal, Image, and Video Technology 39, 49–62 (2005). https://doi.org/10.1023/B:VLSI.0000047271.93455.b8

Published:

Issue Date:

DOI: https://doi.org/10.1023/B:VLSI.0000047271.93455.b8