Abstract

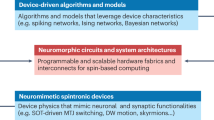

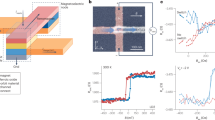

Since the early 1980s, most electronics have relied on the use of complementary metal–oxide–semiconductor (CMOS) transistors. However, the principles of CMOS operation, involving a switchable semiconductor conductance controlled by an insulating gate, have remained largely unchanged, even as transistors are miniaturized to sizes of 10 nanometres. We investigated what dimensionally scalable logic technology beyond CMOS could provide improvements in efficiency and performance for von Neumann architectures and enable growth in emerging computing such as artifical intelligence. Such a computing technology needs to allow progressive miniaturization, reduce switching energy, improve device interconnection and provide a complete logic and memory family. Here we propose a scalable spintronic logic device that operates via spin–orbit transduction (the coupling of an electron’s angular momentum with its linear momentum) combined with magnetoelectric switching. The device uses advanced quantum materials, especially correlated oxides and topological states of matter, for collective switching and detection. We describe progress in magnetoelectric switching and spin–orbit detection of state, and show that in comparison with CMOS technology our device has superior switching energy (by a factor of 10 to 30), lower switching voltage (by a factor of 5) and enhanced logic density (by a factor of 5). In addition, its non-volatility enables ultralow standby power, which is critical to modern computing. The properties of our device indicate that the proposed technology could enable the development of multi-generational computing.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 51 print issues and online access

$199.00 per year

only $3.90 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the findings of this study are available from the corresponding author on reasonable request.

References

Kuhn, K. J. Considerations for ultimate CMOS scaling. IEEE Trans. Electron Dev. 59, 1813–1828 (2012).

Ferain, I., Colinge, C. A. & Colinge, J.-P. Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors. Nature 479, 310–316 (2011).

Auth, C. et al. A 10 nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, self-aligned quad patterning, contact over active gate and cobalt local interconnects. In Electron Devices Meeting 2017, 29.1.1–29.1.4 (IEEE, 2017).

Moore, G. E. Cramming more components onto integrated circuits. Proc. IEEE 86, 82–85 (1998).

Dennard, R. H., Gaensslen, F. H., Yu, H. N., Rideout, V. L., Bassous, E. & Leblanc, A. R. Design of ion-implanted MOSFET’s with very small physical dimensions. IEEE J. Solid St. Circ. 9, 256–268 (1974).

Ghani, T. et al. A 90 nm high volume manufacturing logic technology featuring novel 45nm gate length strained silicon CMOS transistors. In Electron Devices Meeting 2003, 11.6.1–11.6.3 (IEEE, 2003).

Krishnamohan, T. et al. Comparison of (001), (110) and (111) uniaxial- and biaxial- strained-Ge and strained-Si PMOS DGFETs for all channel orientations: mobility enhancement, drive current, delay and off-state leakage. In Electron Devices Meeting 2008, 1–4 (IEEE, 2008).

Huang, X. et al. Sub 50-nm FinFET: PMOS. In Electron Devices Meeting 1998, 67–70 (IEEE, 1999).

Schumacher, M., Baumann, P. K. & Seidel, T. AVD and ALD as two complementary technology solutions for next generation dielectric and conductive thin-film processing. Chem. Vap. Depos. 12, 99–108 (2006).

Horowitz, M. Computing's energy problem (and what we can do about it). In Solid-State Circuits Conference Digest of Technical Papers 2014 10–14 (IEEE, 2014).

Theis, T. N. & Solomon, P. M. It’s time to reinvent the transistor! Science 327, 1600–1601 (2010).

Nikonov, D. E. & Young, I. A., Benchmarking of beyond-CMOS exploratory devices for logic integrated circuits. IEEE J. Explor. Solid-State Computat. Devices Circuits 1, 3–11 (2015).

Manipatruni, S., Nikonov, D. E. & Young, I. A. Beyond CMOS computing with spin and polarization. Nat. Phys. 14, 338 (2018).

Zografos, O. et al. Design and benchmarking of hybrid CMOS-spin wave device circuits compared to 10 nm CMOS. In 2015 IEEE 15th International Conference on Nanotechnology (IEEE-NANO), 686–689 (IEEE, 2015).

Ma, K. et al. Nonvolatile processor architecture exploration for energy-harvesting applications. IEEE Micro 35, 32–40 (2015).

Mead, C. Neuromorphic electronic systems. Proc. IEEE 78, 1629–1636 (1990).

Patil, A. D., Manipatruni, S., Nikonov, D., Young, I. A. & Shanbhag, N. R. 2017. Shannon-inspired statistical computing to enable spintronics. Preprint at https://arxiv.org/abs/1702.06119 (2017).

Dyakonov, M. I. & Perel, V. I. Current-induced spin orientation of electrons in semiconductors. Phys. Lett. A 35, 459 (1971).

Edelstein, V. M. Spin polarization of conduction electrons induced by electric current in two-dimensional asymmetric electron systems. Solid State Commun. 73, 233–235 (1990).

Soumyanarayanan, A., Reyren, N., Fert, A. & Panagopoulos, C. Emergent phenomena induced by spin–orbit coupling at surfaces and interfaces. Nature 539, 509 (2016).

Hsieh, D. et al. A tunable topological insulator in the spin helical Dirac transport regime. Nature 460, 1101 (2009).

Rojas Sánchez, J. C. et al. Spin-to-charge conversion using Rashba coupling at the interface between non-magnetic materials. Nat. Commun. 4, 2944 (2013).

Shen, K., Vignale, G. & Raimondi, R. Microscopic theory of the inverse Edelstein effect. Phys. Rev. Lett. 112, 096601 (2014).

Shiomi, Y. et al. Spin–electricity conversion induced by spin injection into topological insulators. Phys. Rev. Lett. 113, 196601 (2014).

Varignon, J., Vila, L., Barthelemy, A. & Bibes, M. A new spin for oxide interfaces. Nat. Phys. 14, 322 (2018).

Spaldin, N. A. & Fiebig, M. The renaissance of magnetoelectric multiferroics. Science 309, 391–392 (2005).

Heron, J. T. et al. Deterministic switching of ferromagnetism at room temperature using an electric field. Nature 516, 370–373 (2014).

Cherifi, R. O. et al. Electric-field control of magnetic order above room temperature. Nat. Mater. 13, 345–351 (2014).

He, X. et al. Robust isothermal electric control of exchange bias at room temperature. Nat. Mater. 9, 579–585 (2010).

Manipatruni, S. et al. Voltage control of uni-directional anisotropy in ferromagnet–multiferroic system. Preprint at https://arxiv.org/abs/1801.08280 (2018).

Brataas, A., Bauer, G. E. & Kelly, P. J. Non-collinear magnetoelectronics. Phys. Rep. 427, 157–255 (2006).

Manipatruni, S., Nikonov, D. E. & Young, I. A. Modeling and design of spintronic integrated circuits. IEEE Trans. Circuits Syst. 59, 2801–2814 (2012).

Omori, Y. et al. Inverse spin Hall effect in a closed loop circuit. Appl. Phys. Lett. 104, 242415 (2014).

Fan, Y. et al. Magnetization switching through giant spin–orbit torque in a magnetically doped topological insulator heterostructure. Nat. Mater. 13, 699 (2014).

Mahendra, D. C. et al. Room-temperature perpendicular magnetization switching through giant spin-orbit torque from sputtered BixSe(1−x) topological insulator material. Preprint at https://arxiv.org/abs/1703.03822 (2017).

Lesne, E. et al. Highly efficient and tunable spin-to-charge conversion through Rashba coupling at oxide interfaces. Nat. Mater. 15, 1261–1266 (2016).

Ast, C. R. et al. Giant spin splitting through surface alloying. Phys. Rev. Lett. 98, 186807 (2007).

Veit, M. J., Arras, R., Ramshaw, B. J., Pentcheva, R. & Suzuki, Y. Nonzero Berry phase in quantum oscillations from giant Rashba-type spin splitting in LaTiO3/SrTiO3 heterostructures. Nat. Commun. 9, 1458 (2018).

Meindl, J. D., Chen, Q. & Davis, J. A. Limits on silicon nanoelectronics for terascale integration. Science 293, 2044–2049 (2001).

Manipatruni, S., Lipson, M. & Young, I. A. Device scaling considerations for nanophotonic CMOS global interconnects. IEEE J. Sel. Topics Quantum Electron. 19, 8200109 (2013).

Mayadas, A. F., Shatzkes, M. & Janak, J. F. Electrical resistivity model for polycrystalline films: the case of specular reflection at external surfaces. Appl. Phys. Lett. 14, 345–347 (1969).

Chu, Y. H. et al. Low voltage performance of epitaxial BiFeO3 films on Si substrates through lanthanum substitution. Appl. Phys. Lett. 92, 102909 (2008).

Gardner, D. S., Meindl, J. D. & Saraswat, K. C. Interconnection and electro migration scaling theory. IEEE Trans. Electron Dev. 34, 633–643 (1987).

Karube, S., Kondou, K. & Otani, Y. 2016. Experimental observation of spin to charge current conversion at non-magnetic metal/Bi2O3 interfaces. Preprint at https://arxiv.org/abs/1601.04292 (2016).

Pesin, D. & Balents, L. Mott physics and band topology in materials with strong spin–orbit interaction. Nat. Phys. 6, 376 (2010).

Rojas-Sánchez, J.-C. et al. Spin to charge conversion at room temperature by spin pumping into a new type of topological insulator: α-Sn films. Phys. Rev. Lett. 116, 096602 (2016).

Khang, N. H. D., Ueda, Y. & Hai, P. N. A conductive topological insulator with large spin Hall effect for ultralow power spin–orbit torque switching. Nat. Mater. 17, 808–813 (2018).

Cheng, C. et al. Direct observation of spin-to-charge conversion in MoS2 monolayer with spin pumping. Preprint at https://arxiv.org/abs/1510.03451 (2015).

Wang, G. et al. Spin–orbit engineering in transition metal dichalcogenide alloy monolayers. Nat. Commun. 6, 10110 (2015).

Kimura, T., Goto, T., Shintani, H., Ishizaka, K., Arima, T. & Tokura, Y. Magnetic control of ferroelectric polarization. Nature 426, 55–58 (2003).

Mundy, J. A. et al. Atomically engineered ferroic layers yield a room-temperature magnetoelectric multiferroic. Nature 537, 523 (2016).

Srisukhumbowornchai, N. & Guruswamy, S. Large magnetostriction in directionally solidified FeGa and FeGaAl alloys. J. Appl. Phys. 90, 5680–5688 (2001).

Ryu, J., et al. Magnetoelectric properties in piezoelectric and magnetostrictive laminate composites. Jpn J. Appl. Phys. 40, 4948 –4951 (2001).

Street, M. et al. Increasing the Néel temperature of magnetoelectric chromia for voltage-controlled spintronics. Appl. Phys. Lett. 104, 222402 (2014).

Wang, J. et al. Magnetoelectric Fe2TeO6 thin films. J. Phys. Condens. Matter 26, 055012 (2014).

Behin-Aein, B., Datta, D., Salahuddin, S. & Datta, S. Proposal for an all-spin logic device with built-in memory. Nat. Nanotechnol. 5, 266–270 (2010).

Nikonov, D. E., Bourianoff, G. I. & Ghani, T. Proposal of a spin torque majority gate logic. IEEE Electron Device Lett. 32, 1128–1130 (2011).

Manipatruni, S., Nikonov, D. E. & Young, I. A. Material targets for scaling all-spin logic. Phys. Rev. Appl. 5, 014002 (2016).

Imre, A. et al. Majority logic gate for magnetic quantum-dot cellular automata. Science 311, 205–208 (2006).

Chumak, A. V., Serga, A. A. & Hillebrands, B. Magnon transistor for all-magnon data processing. Nat. Commun. 5, 4700 (2014).

Ionescu, A. M. & Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329–337 (2011).

Lu, H. & Seabaugh, A. Tunnel field-effect transistors: state-of-the-art. IEEE J. Electron Devices Soc. 2, 44–49 (2014).

Salahuddin, S. & Datta, S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 8, 405–410 (2008).

Newns, D., Elmegreen, B., Liu, X. H. & Martyna, G. A low-voltage high-speed electronic switch based on piezoelectric transduction. J. Appl. Phys. 111, 084509 (2012).

Son, J., Rajan, S., Stemmer, S. & Allen, S. J. A heterojunction modulation-doped Mott transistor. J. Appl. Phys. 110, 084503 (2011).

Srinivasan, S., Diep, V., Behin-Aein, B., Sarkar, A. & Datta, S. Modeling multi-magnet networks interacting via spin currents. In Handbook of Spintronics 1281–1335 (2016).

Apalkov, D. M. & Visscher, P. B. Spin-torque switching: Fokker–Planck rate calculation. Phys. Rev. B 72, 180405 (2005).

Butler, W. H. et al. Switching distributions for perpendicular spin-torque devices within the macrospin approximation. IEEE Trans. Magnet. 48, 4684–4700 (2012).

Shannon, C. E. A universal Turing machine with two internal states. Automata Stud. 34, 157–165 (1957).

Amarù, L. et al. Majority logic synthesis. In Proc. International Conference on Computer-Aided Design 79 (ACM, 2018).

Manipatruni, S., Nikonov, D. E. & Young, I. A. All-spin nanomagnetic state elements. Appl. Phys. Lett. 103, 063503 (2013).

Dutta, S. et al. Highly scaled ruthenium interconnects. IEEE Electron Dev. Lett. 38, 949–951 (2017).

Dutta, S. et al. Sub-100 nm2 cobalt interconnects. IEEE Electron Dev. Lett. 39, 731–734 (2018).

Acknowledgements

We are grateful to A. Fert and J.-P. Wang for discussions. We acknowledge F. Rana, D. Schlom and F. Casanova for insights shared with us. We also acknowledge the support of K. Oguz and B. Buford of Intel Corporation for discussions on device integration and metrology. R.R. acknowledges the long-term support of the Quantum Materials programme funded by the US Department of Energy, Office of Basic Energy Sciences, which laid the foundation for the key elements of the work reported in this paper. B.P., Y.-L.H. and R.R. acknowledge support from Semiconductor Research Corporation within the JUMP program.

Reviewer information

Nature thanks V. Bertacco, Y. Otani and the other anonymous reviewer(s) for their contribution to the peer review of this work.

Author information

Authors and Affiliations

Contributions

S.M. identified the use of the inverse spin–orbit effect for electrically transduced spin-logic devices. S.M., D.E.N. and I.A.Y. developed the logic circuits. S.M. developed the scaling laws, physical macro models and interconnect estimates. H.L. developed circuit design techniques and performed the logic-circuit simulations with the physical macro models. S.M. and R.R. developed the material scaling options and coordinated the material growth. S.M. conceptualized the test devices and designed the experiments and measurements for the magnetoelectric and spin–orbit devices. D.E.N. benchmarked the performance of the circuits. C.-C.L., B.P. and T.G. performed the layout of the test devices, processed the devices and identified processing methods for sub-micron-sized magnetoelectric and spin–orbit devices. S.M. and E.B. measured the magnetoelectric devices. S.M. and T.G. measured the spin–orbit devices. B.P., Y.-L.H. and E.B. deposited the samples and performed material characterization under the supervision of R.R. S.M. wrote the manuscript and D.E.N., I.A.Y. and R.R. edited the manuscript. All authors reviewed the manuscript and interpreted the data.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

This file contains a Supplementary Guide and Supplementary Text sections A to Q, which includes Supplementary Figs. 1 to 24 and Supplementary Tables 1 to 4.

Rights and permissions

About this article

Cite this article

Manipatruni, S., Nikonov, D.E., Lin, CC. et al. Scalable energy-efficient magnetoelectric spin–orbit logic. Nature 565, 35–42 (2019). https://doi.org/10.1038/s41586-018-0770-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41586-018-0770-2