Abstract

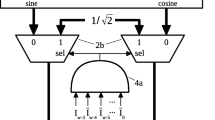

We propose a reconfigurable control-bit generation algorithm for rotation and sub-word rotation operations. The algorithm uses a self-routing characteristic to configure an inverse butterfly network. In addition to being highly parallelized and inexpensive, the algorithm integrates the rotation-shift, bi-directional rotation-shift, and sub-word rotation-shift operations. To our best knowledge, this is the first scheme to accommodate a variety of rotation operations into the same architecture. We have developed the highly efficient reconfigurable rotation unit (HERRU) and synthesized it into the Semiconductor Manufacturing International Corporation (SMIC)’s 65-nm process. The results show that the overall efficiency (relative area×relative latency) of our HERRU is higher by at least 23% than that of other designs with similar functions. When executing the bi-directional rotation operations alone, HERRU occupies a significantly smaller area with a lower latency than previously proposed designs.

Similar content being viewed by others

References

Bansod, G., Raval, N., Pisharoty, N., 2014. Implementation of a new lightweight encryption design for embedded security. IEEE Trans. Inform. Forens. Secur. 10(1): 142–151. https://doi.org/10.1109/TIFS.2014.2365734

Belazi, A., El-Latif, A., Belghith, S., 2016. A novel image encryption scheme based on substitution-permutation network and chaos. Signal Process., 128: 155–170. https://doi.org/10.1016/j.sigpro.2016.03.021

Chang, Z., Hu, J., Zheng, C., et al., 2013. Research on shifter based on iButterfly network. Commun. Comput. Inform. Sci., 396: 92–100. https://doi.org/10.1007/978-3-642-41635-4_10

Dai, H., Shen, X., 2007. Rearrageability of the 7-stage 16×16 shuffle exchange network. Acta Electron. Sin., 35(10): 1875–1891 (in Chinese).

Hilewitz, Y., Lee, R.B., 2006. Fast bit compression and expansion with parallel extract and parallel deposit instructions. IEEE Int. Conf. on Application-Specific Systems, p.65–72. https://doi.org/10.1109/ASAP.2006.33

Hilewitz, Y., Lee, R.B., 2007. Performing advanced bit manipulations efficiently in general-purpose processors. IEEE Symp. on Computer Arithmetic, p.251–260. https://doi.org/10.1109/ARITH.2007.27

Hilewitz, Y., Lee, R.B., 2008. Fast bit gather, bit scatter and bit permutation instructions for commodity microprocessors. J. Signal Process. Syst., 53(2): 145–169. https://doi.org/10.1007/s11265-008-0212-8

Hilewitz, Y., Lee, R.B., 2009. A new basis for shifters in general-purpose processors for existing and advanced bit manipulations. IEEE Trans. Comput., 58(8): 1035–1048. https://doi.org/10.1109/TC.2008.219

Hilewitz, Y., Shi, Z.J., Lee, R.B., 2004. Comparing fast implementations of bit permutation instructions. Proc. 38th Annual Asilomar Conf. on Signals, Systems, and Computers, p.1856–1863. https://doi.org/10.1109/ACSSC.2004.1399486

Intel Corporation, 2006. Intel Itanium Architecture Software Developer’s Manual, Vol. 3, Rev. 2.2. https://www.intel.com/content/www/us/en/processors/itanium/itanium-architecture-vol-3-manual.html [Accessed on April 5, 2016].

Intel Corporation, 2015. Intel® 64 and IA-32 Architectures Software Developer’s Manual. https://software.intel.com/sites/default/files/managed/39/c5/325462-sdm-vol-1-2abcd-3abcd.pdf [Accessed on April 10, 2016].

Jolfaei, A., Wu, X., Muthukkumarasamy, V., 2015. On the security of permutation-only image encryption schemes. IEEE Trans. Inform. Forens. Secur., 11(2): 235–246. https://doi.org/10.1109/TIFS.2015.2489178

Lee, R.B., Shi, Z.J., Yin, Y.L., et al., 2004. On permutation operations in cipher design. Int. Conf. on Information Technology: Coding and Computing, p.569–577. https://doi.org/10.1109/ITCC.2004.1286714

Nassimi, D., Sahni, S., 1981. A self-routing benes network and parallel permutation algorithm. IEEE Trans. Comput., 30(8): 332–340. https://doi.org/10.1109/TC.1981.1675791

Pillmeier, M.R., 2002. Barrel Shifter Design, Optimization, and Analysis. MS Thesis, Lehigh University, Bethlehem, Pennsylvania.

Pillmeier, M.R., Schulte, M.J., Walters, E.G.III, 2002. Design alternatives for barrel shifters. Proc. Advanced Signal Processing Algorithms, Architectures, and Implementations, p.436–447. https://doi.org/10.1117/12.452034

Rajkumar, S., Goyal, N.K., 2014. Design of 4-disjoint gamma interconnection network layouts and reliability analysis of gamma interconnection networks. J. Supercomput., 69(1): 468–491. https://doi.org/10.1007/s11227-014-1175-0

Saraswathi, P.V., Venkatesulu, M., 2014. A block cipher based on Boolean matrices using bit level operations. IEEE/ACIS 13th Int. Conf. on Computer and Information Science, p.59–63. https://doi.org/10.1109/ICIS.2014.6912108

Sayilar, G., Chiou, D., 2015. Cryptoraptor: high-throughput reconfigurable cryptographic processor. IEEE/ACM Int. Conf. on Computer-Aided Design, p.155–161. https://doi.org/10.1109/ICCAD.2014.7001346

Semiconductor Manufacturing International Corporation, 2012. SMIC 55nm Low Leakage Logic Process Standard Cell Library Databook v2.0. http://www.smics.com/eng/design/libraries_smic.php

Shi, Z.J., Yang, X., Lee, R.B., 2008. Alternative applicationspecific processor architectures for fast arbitrary bit permutations. Int. J. Embed. Syst., 3(4): 219–228. https://doi.org/10.1504/IJES.2008.022393

Author information

Authors and Affiliations

Corresponding author

Additional information

Project supported by the National Natural Science Foundation of China (No. 61404175)

About this article

Cite this article

Ma, C., Dai, Zb., Li, W. et al. A highly efficient reconfigurable rotation unit based on an inverse butterfly network. Frontiers Inf Technol Electronic Eng 18, 1784–1794 (2017). https://doi.org/10.1631/FITEE.1601265

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1631/FITEE.1601265