Abstract

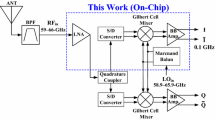

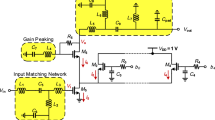

A 19 mW highly integrated GPS receiver with a ΣΔfractional-N synthesizer is presented in this paper. Fractional-N frequency synthesizer architecture was adopted in this work, to provide more degrees of freedom in the synthesizer design. A high linearity low noise amplifier (LNA) is integrated into the chip. The radio receiver chip was fabricated in a 0.18 μm complementary metal oxide semiconductor (CMOS) process and packaged in a 48-pin 2 mm×2 mm land grid array chip scale package. The chip consumes 19 mW (LNA1 excluded) and the LNA1 6.3 mW. Measured performances are: noise figure<2 dB, channel gain=108 dB (LNA1 included), image rejection>36 dB, and −108 dBc/Hz @ 1 MHz phase noise offset from the carrier. The carrier noise ratio (C/N) can reach 41 dB at an input power of −130 dBm. The chip operates over a temperature range of [−40, 120] °C and ±5% tolerance over the CMOS technology process.

Similar content being viewed by others

References

Aloi, D.N., Alsliety, M., Akos, D.M., Rochester, M., 2007. A methodology for the evaluation of a GPS receiver performance in telematics applications. IEEE Trans. Instrum. Meas., 56(1):11–24. [doi:10.1109/TIM.2006.887190]

Bruzdzinski, J., Gronicz, J., Aaltonen, L., Halonen, K., 2008. Behavioral Simulation of Fractional-N PLL Frequency Synthesizers: Phase Approach. IEEE 11th Int. Biennial Baltic Electronics Conf., p.121–124. [doi:10.1109/BEC. 2008.4657493]

Chung, S.I., Lee, H.S., Lee, H.H., 2008. A Study on the In-Orbit Environment of a GPS Receiver for Low/Medium Altitude Satellites. 6th IEEE Int. Conf. on Industrial Informatics, p.694–699. [doi:10.1109/INDIN.2008.4618190]

Di, L., 2008. An Integrated GPS Receiver Front-End Design. China Patent ZL 200720032070.0 (in Chinese).

Gramegna, G., Mattos, P.G., Losi, M., Das, S., Franciotta, M., Bellantone, N.G., Vaiana, M., Mandara, V., Paparo, M., 2006. A 56-mW 23-mm2 single-chip 180-nm CMOS GPS receiver with 27.2-mW 4.1-mm2 radio. IEEE J. Sol.-State Circuits, 41(3):540–551. [doi:10.1109/JSSC.2005.864136]

Huang, S.L., Ma, H.N., Wang, Z.H., 2007. Modeling and Simulation to the Design of Sigma-Delta Fractional-N Frequency Synthesizer. IEEE Design, Automation and Test in Europe Conf. and Exhibition, p.291–296. [doi:10.1109/DATE.2007.364606]

IEEE Global History Network, 2008. Citing IEEE org. IEEE Xplore Digital Library. Available from http://www.ieeeghn.org/wiki/index.php/Global_Positioning_System [Accessed on Apr. 30, 2009].

Kim, J.M., Song, H.J., Kim, Y.B., 1999. Design and Implementation of L1-Band C/A-Code GPS RF Front-End Chip. 6th Int. Conf. on VLSI and CAD, p.372–375. [doi:10.1109/ICVC.1999.820934]

Liu, L.Y., Amin, M.G., 2008. Performance analysis of GPS receivers in non-Gaussian noise incorporating precorrelation filter and sampling rate. IEEE Trans. Signal Process., 56(3):990–1004. [doi:10.1109/TSP.2006.890827]

Magoon, R., Molnar, A., Zachan, J., Hatcher, G., Rhee, W., 2002. A single-chip quad-band (850/900/1800/1900 MHz) direct conversion GSM/GPRS RF transceiver with integrated VCOs and fractional-N synthesizer. IEEE J. Sol.-State Circuits, 37(12):1710–1720. [doi:10.1109/JSSC.2002.804356]

Peczalski, A., 2002. RF/Analog/Digital SOI Technology for GPS Receivers and Other Systems on a Chip. IEEE Aerospace Conf. Proc., 4:2013–2017. [doi:10.1109/AERO. 2002.1036913]

Rhee, W., Song, B.S., Ali, A., 2000. A 1.1-GHz CMOS fractional-N frequency synthesizer with a 3-b third-order ΣΔ modulator. IEEE J. Sol.-State Circuits, 35(10):1453–1458. [doi:10.1109/4.871322]

Ti, C.H., Liu, Y.H., Lin, Y.H., 2008. A 2.4-GHz Fractional-N PLL with a PDF/CP Linearization and an Improved CP Circuit. IEEE Int. Symp. on Circuits and Systems, p.1728–1731. [doi:10.1109/ISCA.2008.451771]

Tsui, J.B.Y., Akos, D.M., 1996. Comparison of Direct and Down-Converted Digitization in GPS Receiver Front End Designs. Microwave Symp. Digest, IEEE MTT-S Int., 3:1343–1346. [doi:10.1109/MWSYM.1996.512184]

Wang, E.S., Zhang, S.F., Hu, Q., Yi, J., Sun, X.W., 2008. Implementation of an Embedded GPS Receiver Based on FPGA and Micro Blaze. 4th IEEE Int. Conf. on Wireless Communications, Networking and Mobile Computing, p.1–4. [doi:10.1109/WiCom.2008.335]

Xiao, P., Thomsen, A., Abraham, J., 2008. Improving Bandwidth while Managing Phase Noise and Spurs in Fractional-N PLL. IEEE Computer Society Annual Symp. on VLSI, p.168–172. [doi:10.1109/ISVLSI.2008.47]

Zhu, Y.H., Shao, Z.B., Pang, W.Y., 2004. A generalized MASH architecture in fractional-N synthesizer. IEEE J. Sol.-State Circuits, 2:1512–1515. [doi:10.1109/ICSICT.2004.1436 899]

Author information

Authors and Affiliations

Corresponding author

Additional information

Project supported by the National Natural Science Foundation of China (Nos. 60725415 and 60971066) and the National High-Tech R & D Program (863) of China (Nos. 2009AA01Z258 and 2009AA 01Z260)

Rights and permissions

About this article

Cite this article

Li, D., Yang, Yt., Wang, Ja. et al. Design of a low power GPS receiver in 0.18 μm CMOS technology with a ΣΔfractional-N synthesizer. J. Zhejiang Univ. - Sci. C 11, 444–449 (2010). https://doi.org/10.1631/jzus.C0910381

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1631/jzus.C0910381