Abstract

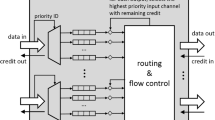

The network-on-chip (NoC) architecture is a main factor affecting the system performance of complicated multi-processor systems-on-chips (MPSoCs). To evaluate the effects of the NoC architectures on communication efficiency, several kinds of techniques have been developed, including various simulators and analytical models. The simulators are accurate but time consuming, especially in large space explorations of diverse network configurations; in contrast, the analytical models are fast and flexible, providing alternative methods for performance evaluation. In this paper, we propose a general analytical model to estimate the communication performance for arbitrary NoCs with wormhole routing and virtual channel flow control. To resolve the inherent dependency of successive links occupied by one packet in wormhole routing, we propose the routing path decomposition approach to generating a series of ordered link categories. Then we use the traditional queuing system to derive the fine-grained transmission latency for each network component. According to our experiments, the proposed analytical model provides a good approximation of the average packet latency to the simulation results, and estimates the network throughput precisely under various NoC configurations and workloads. Also, the analytical model runs about 105 times faster than the cycle-accurate NoC simulator. Practical applications of the model including bottleneck detection and virtual channel allocation are also presented.

Similar content being viewed by others

References

Arjomand, M., Sarbazi-Azad, H., 2009. A Comprehensive Power-Performance Model for NoCs with Multi-flit Channel Buffers. Proc. 23rd Int. Conf. on Super-computing, p.470–478. [doi:10.1145/1542275.1542341]

Bahn, J.H., Bagherzadeh, N., 2008. Design of simulation and analytical models for a 2D-meshed asymmetric adaptive router. IET Comput. Digit. Techn., 2(1):63–73. [doi:10.1049/iet-cdt:20070043]

Ciciani, B., Colajanni, M., Paolucci, C., 1997. An Accurate Model for the Performance Analysis of Deterministic Wormhole Routing. Proc. 11th Int. Parallel Processing Symp., p.353–359. [doi:10.1109/IPPS.1997.580926]

Dally, W.J., 1992. Virtual-channel flow control. IEEE Trans. Parall. Distr. Syst., 3(2):194–205. [doi:10.1109/71.127260]

Draper, J.T., Ghosh, J., 1994. A comprehensive analytical model for wormhole routing in multicomputer systems. J. Parall. Distr. Comput., 23(2):202–214. [doi:10.1006/jpdc.1994.1132]

Guz, Z., Walter, I., Bolotin, E., Cidon, I., Ginosar, R., Kolodny, A., 2006. Efficient Link Capacity and QoS Design for Network-on-Chip. Proc. Design, Automation and Test in Europe, p.1–6. [doi:10.1109/DATE.2006.243951]

Hu, J.C., Ogras, U.Y., Marculescu, R., 2006. System-level buffer allocation for application-specific networks-on-chip router design. IEEE Trans. Comput.-Aid. Des. Integr. Circ. Syst., 25(12):2919–2933. [doi:10.1109/TCAD.2006.882474]

Hu, P.C., Kleinrock, L., 1997. An Analytical Model for Wormhole Routing with Finite Size Input Buffers. Proc. 15th Int. Teletraffic Congress, p.549–560. [doi:10.1016/S1388-3437(97)80058-3]

Keutzer, K., Newton, A.R., Rabaey, J.M., Sangiovanni-Vincentelli, A., 2000. System-level design: orthogonalization of concerns and platform-based design. IEEE Trans. Comput.-Aid. Des. Integr. Circ. Syst., 19(12): 1523–1543. [doi:10.1109/43.898830]

Krimer, E., Erez, M., Keslassy, I., Kolodny, A., Walter, I., 2009. Packet-Level Static Timing Analysis for NoCs. Proc. 3rd ACM/IEEE Int. Symp. on Networks-on-Chip, p.88. [doi:10.1109/NOCS.2009.5071451]

Li, S., Peh, L.S., Jha, N.K., 2003. Dynamic Voltage Scaling with Links for Power Optimization of Interconnection Networks. Proc. 9th Int. Symp. on High-Performance Computer Architecture, p.91–102. [doi:10.1109/HPCA.2003.1183527]

Lu, C.L., 2009. Queuing Theory (2nd Ed.). Beijing University of Posts and Telecommunications Press, Beijing, China, p.32–41 (in Chinese).

Marculescu, R., Bogdan, P., 2009. The chip is the network: toward a science of network-on-chip design. Found. Trends Electron. Des. Automat., 2(4):371–461. [doi:10.1561/1000000011]

Marculescu, R., Ogras, U.Y., Peh, L.S., Jerger, N.E., Hoskote, Y., 2009. Outstanding research problems in NoC design: system, microarchitecture, and circuit perspectives. IEEE Trans. Comput.-Aid. Des. Integr. Circ. Syst., 28(1):3–21. [doi:10.1109/TCAD.2008.2010691]

Moadeli, M., Shahrabi, A., Vanderbauwhede, W., 2007a. Analytical Modelling of Communication in the Rectangular Mesh NoC. Int. Conf. on Parallel and Distributed Systems, p.1–8. [doi:10.1109/ICPADS.2007.4447826]

Moadeli, M., Shahrabi, A., Vanderbauwhede, W., Ould-Khaoua, M., 2007b. An Analytical Performance Model for the Spidergon NoC. IEEE 21st Int. Conf. on Advanced Information Networking and Applications, p.1014–1021. [doi:10.1109/AINA.2007.31]

Moraveji, R., Moinzadeh, P., Sarbazi-Azad, H., 2008. A General Approach for Analytical Modeling of Irregular NoCs. IEEE Int. Symp. on Parallel and Distributed Processing with Applications, p.327–334. [doi:10.1109/ISPA.2008.109]

Moraveji, R., Moinzadeh, P., Sarbazi-Azad, H., 2009. A general mathematical performance model for wormhole-switched irregular networks. Clust. Comput., 12(3):285–297. [doi:10.1007/s10586-009-0084-0]

Ni, L.M., McKinley, P.K., 1993. A survey of wormhole routing techniques in direct networks. Computer, 26(2):62–76. [doi:10.1109/2.191995]

Ogras, U.Y., Marculescu, R., 2007. Analytical Router Modeling for Networks-on-Chip Performance Analysis. Proc. Design, Automation and Test in Europe, p.1096–1101. [doi:10.1109/DATE.2007.364440]

Ould-Khaoua, M., Sarbazi-Azad, H., 2001. An analytical model of adaptive wormhole routing in hypercubes in the presence of hot spot traffic. IEEE Trans. Parall. Distr. Syst., 12(3):283–292. [doi:10.1109/71.914770]

Sarbazi-Azad, H., 2003. A mathematical model of deterministic wormhole routing in hypercube multi-computers using virtual channels. Appl. Math. Model., 27(12):943–953. [doi:10.1016/S0307-904X(03)00135-5]

Sarbazi-Azad, H., Ould-Khaoua, M., Mackenzie, L.M., 2001. An accurate analytical model of adaptive wormhole routing in k-ary n-cubes interconnection networks. Perform. Eval., 43(2–3):165–179.

Author information

Authors and Affiliations

Corresponding author

Additional information

Project supported by the National High-Tech Research and Development Program (863) of China (No. 2009AA011706) and the Fundamental Research Funds for the Central Universities, China

Rights and permissions

About this article

Cite this article

Cheng, Al., Pan, Y., Yan, Xl. et al. A general communication performance evaluation model based on routing path decomposition. J. Zhejiang Univ. - Sci. C 12, 561–573 (2011). https://doi.org/10.1631/jzus.C1000281

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1631/jzus.C1000281

Key words

- Analytical model

- Communication performance

- Network-on-chip (NoC)

- Queuing system

- Routing path decomposition

- Virtual channel