Abstract

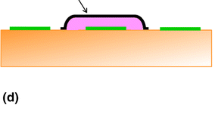

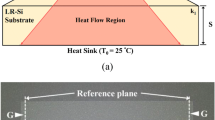

With the development of 3D integration technology, microsystems with vertical interconnects are attracting attention from researchers and industry applications. Basic elements of integrated passive devices (IPDs), including inductors, capacitors, and resistors, could dramatically save the footprint of the system, optimize the form factor, and improve the performance of radio frequency (RF) systems. In this paper, IPDs using thin film built-up technology are introduced, and the design and characterization of coplanar waveguides (CPWs), inductors, and capacitors are presented.

Similar content being viewed by others

References

Arcioni, P., Castello, R., de Astis, G., Sacchi, E., Svelto, F., 1998. Measurement and modeling of Si integrated inductors. IEEE Trans. Instrum. Meas., 47(5):1372–1378. [doi:10.1109/19.746613]

Ashby, K.B., Koullias, I.A., Finley, W.C., Bastek, J.J., Moinian, S., 1996. High Q inductors for wireless applications in a complementary silicon bipolar process. IEEE J. Sol.-State Circ., 31(1):4–9. [doi:10.1109/4.485838]

Baron, J., Garrou, P., Pizzagalli, A., 2012. Polymeric Materials for 3DIC & Wafer-Level Packaging Applications (Sample Presentation). Available form http://www.i-micronews.com [Accessed on July 31, 2012].

Beyne, E., 2008. Solving Technical and Economical Barriers to the Adoption of Through-Si-Via 3D Integration Technologies. 10 th Electronics Packaging Technology Conf., p.29–34. [doi:10.1109/EPTC.2008.4763408]

Cui, Q., Sun, X., Zhu, Y., Ma, S., Chen, J., Miao, M., Jin, Y., 2011. Design and Optimization of Redistribution Layer (RDL) on TSV Interposer for High Frequency Applications. IEEE Int. Conf. on Electronic Packaging Technology & High Density Packaging, p.1–5. [doi:10.1109/ICEPT.2011.6066788]

Eisenstadt, W.R., Eo, Y., 1992. S-parameter-based IC interconnect transmission line characterization. IEEE Trans. Compon. Hybr. Manuf. Technol., 15(4):483–490. [doi:10. 1109/33.159877]

Frickey, D.A., 1994. Conversions between S, Z, Y, H, ABCD, and T parameters which are valid for complex source and load impedances. IEEE Trans. Microw. Theory Techn., 42(2):205–211. [doi:10.1109/22.275248]

Kim, H., Eo, Y., 2008. High-frequency-measurement-based circuit modeling and power/ground integrity evaluation of integrated circuit packages. IEEE Trans. Adv. Pack., 31(4):910–918. [doi:10.1109/TADVP.2008.2005472]

Leung, L.L.W., Hon, W.C, Chen, K.J., 2004. Low-loss coplanar waveguides interconnects on low-resistivity silicon substrate. IEEE Trans. Compon. Pack. Technol., 27(3): 507–512. [doi:10.1109/TCAPT.2004.831780]

Liu, K., Frye, R., Hlaing, M., Lee, Y., Kim, H., Kim, G., Ahn, B., 2012. Investigation of Integrated Passive Device with Through-Silicon Via. IEEE 62nd Electronic Components and Technology Conf., p.1833–1839. [doi:10.1109/ECTC. 2012.6249087]

Lu, J., 2009. 3-D hyperintegration and packaging technologies for micro-nano systems. Proc. IEEE, 97(1):18–30. [doi:10. 1109/JPROC.2008.2007458]

Mi, X., Takahashi, T., Ueda, S., 2008. Integrated Passives on LTCC for Achieving Chip-Sized-Modules. 38th European Microwave Conf., p.607–610. [doi:10.1109/EUMC.2008.4751525]

Ramm, P., Klumpp, A., Weber, J., Lietaer, N., Taklo, M., de Raedt, W., Fritzsch, T., Couderc, P., 2010. 3D Integration Technology: Status and Application Development. Proc. ESSCIRC, p.9–16. [doi:10.1109/ESSCIRC.2010.5619857]

Siew, G., Soh, S., Tee, T.Y., Chen, H., Kang, I.S., Kim, J.H., 2011. Electrical Simulation and Measurement of IPD with Multilayer Thin Film Technology for WLP. IEEE Int. Conf. on Electronic Packaging Technology & High Density Packaging, p.659–664. [doi:10.1109/ICEPT.2011.6066918]

Sun, X., Ji, M., Ma, S., Zhu, Y., Kang, W., Miao, M., Jin, Y., 2010. Electrical Characterization of Sidewall Insulation Layer of TSV. 11th Int. Conf. on Electronic Packaging Technology & High Density Packaging, p.77–80. [doi:10.1109/ICEPT.2010.5582360]

Töpper, M., Fischer, T., Baumgartner, T., Reichl, H., 2010. A Comparison of Thin Film Polymers for Wafer Level Packaging. 60th Electronic Components and Technology Conf., p.769–776. [doi:10.1109/ECTC.2010.5490751]

Yook, J., Kim, J.C., Park, S., Ryu, J., Park, J.C., 2012. High Density and Low-Cost Silicon Interposer Using Thin-film and Organic Lamination Processes. IEEE 62nd Electronic Components and Technology Conf., p.274–278. [doi:10.1109/ECTC.2012.6248840]

Zhan, C., Tzeng, P., Lau, J.H., Dai, M., Chien, H., Lee, C., Wu, S., Kao, K., Huang, S., Fan, C., et al., 2012. Assembly Process and Reliability Assessment of TSV/RDL/IPD Interposer with Multi-Chip-Stacking for 3D IC Integration SiP. IEEE 62nd Electronic Components and Technology Conf., p.548–554. [doi:10.1109/ECTC.2012.6248883]

Zinck, C., 2010. 3D Integration Infrastructure & Market Status. IEEE Int. 3D Systems Integration Conf., p.1–34. [doi:10.1109/3DIC.2010.5751425]

Author information

Authors and Affiliations

Corresponding author

Additional information

Project (No. 2009ZX02038) supported by the National Science and Technology Major Project of China

Rights and permissions

About this article

Cite this article

Sun, X., Zhu, Yh., Liu, Zh. et al. Electrical characterization of integrated passive devices using thin film technology for 3D integration. J. Zhejiang Univ. - Sci. C 14, 235–243 (2013). https://doi.org/10.1631/jzus.C12MNT01

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1631/jzus.C12MNT01