Abstract

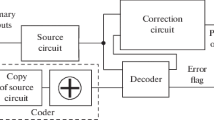

We consider the problem of designing a built-in control circuit with full self-testability of control equipment based on the method of Boolean complement to constant-weight 1-out-of-n codes. A method is proposed for determining complementary functions considering the formation of the necessary set of test combinations for a complete check of each element of modulo-2 addition in the structure of the Boolean complement block. Due to the introduction of uncertainties in the selection of values, it is possible to minimize the complexity of control functions, which makes it possible to simplify the control logic block. An algorithm for the synthesis of a built-in self-test control circuit based on the method of Boolean complement to a preselected constant-weight 1-out-of-n code is given.

Similar content being viewed by others

REFERENCES

Goessel, M. and Graf, S., Error Detection Circuits, London: McGraw-Hill, 1994.

Pradhan, D.K., Fault-Tolerant Computer System Design, New York: Prentice Hall, 1996.

Wang, L.-T., Stroud, C.E., and Touba, N.A., System-On-Chip Test Architectures: Nanometer Design for Testability, Morgan Kaufmann Publishers, 2008.

Ubar, R., Raik, J., and Vierhaus, H.-T., Design and Test Technology for Dependable Systems-On-Chip, New York: IGI Global, 2011.

Kharchenko, V., Kondratenko, Yu., and Kacprzyk, J., Green IT Engineering: Concepts, Models, Complex Systems Architectures, Springer, 2017. https://doi.org/10.1007/978-3-319-44162-7

Busaba, F.Y. and Lala, P.K., Self-checking combinational circuit design for single and unidirectional multibit errors, J. Electron Test.: Theory Appl., 1994, no. 1, pp. 19–28. https://doi.org/10.1007/BF00971960

Piestrak, S.J., Design of Self-Testing Checkers for Unidirectional Error Detecting Codes, Wroclaw: Oficyna Wydawnicza Politechniki Wroclavskiej, 1995.

Nicolaidis, M. and Zorian, Y., On-line testing for VLSI—a compendium of approaches, J. Electron. Test.: Theory Appl., 1998, no. 12, pp. 7–20. https://doi.org/10.1023/A:1008244815697

Das, D. and Touba, N.A., Weight-based codes and their application to concurrent error detection of multilevel circuits, Proceedings of the 17th IEEE VLSI Test Symposium, USA, CA, Dana Point, April 25–29,1999, pp. 370–376.

Matrosova, A.Yu., Levin, I., and Ostanin, S.A., Self-checking synchronous FSM network design with low overhead, VLSI Des., 2000, vol. 11, no. 1, pp. 47–58. https://doi.org/10.1155/2000/46578

Mitra, S. and McCluskey, E.J., Which concurrent error detection scheme to choose?, Proceedings of International Test Conference,2000, Atlantic City, NJ, 2000, pp. 985–994. https://doi.org/10.1109/TEST.2000.894311

Ghosh, S., Basu, S., and Touba, N.A., Synthesis of low power CED circuits based on parity codes, Proceedings of 23rd IEEE VLSI Test Symposium (VTS’05), 2005, pp. 315–320.

Freiman, C.V., Optimal error detection codes for completely asymmetric binary channels, Inf. Control, 1962, vol. 5, no. 1, pp. 64–71. https://doi.org/10.1016/S0019-9958(62)90223-1

Sogomonyan, E.S. and Gössel, M., Design of self-testing and on-line fault detection combinational circuits with weakly independent outputs, J. Electron. Test.: Theory Appl., 1993, vol. 4, no. 4, pp. 267–281. https://doi.org/10.1007/BF00971975

Das, D. and Touba, N.A., Synthesis of circuits with low-cost concurrent error detection based on bose-lin codes, J. Electron. Test.: Theory Appl., 1999, vol. 15, nos. 1–2, pp. 145–155. https://doi.org/10.1023/A:1008344603814

Sogomonyan, E.S. and Slabakov, E.V., Samoproveryaemye ustroistva i otkazoustoichivye sistemy (Self-Checking Devices and Fail-Safe Systems), Moscow: Radio i svyaz’, 1989.

Reynolds, D.A. and Metze, G., Fault detection capabilities of alternating logic, IEEE Trans. Comput., 1978, vol. C-27, no. 12, pp. 1093–1098.

Saposhnikov, Vl.V., Dmitriev, A., Goessel, M., and Saposhnikov, V.V., Self-dual parity checking—a new method for on line testing, Proceedings of 14th IEEE VLSI Test Symposium, Princeton, NJ, 1996, pp. 162–168. https://doi.org/10.1109/VTEST.1996.510852

Gessel’, M., Dmitriev, A.V., Sapozhnikov, V.V., and Sapozhnikov, Vl.V., A self-testing structure for functional failure detection in combinational circuits, Avtom. Telemekh., 1999, no. 11, pp. 162–174.

Dmitriev, A., Saposhnikov, V., Saposhnikov, Vl., Goessel, M., Moshanin, V., and Morosov, A., New self-dual circuits for error detection and testing, VLSI Des., 2000, vol. 11, no. 1, pp. 1–21. https://doi.org/10.1155/2000/84720

Gessel’, M., Dmitriev, A.V., Sapozhnikov, V.V., and Sapozhnikov, Vl.V., Fault detection in combinational circuits using self-dual control, Avtom. Telemekh., 2000, no. 7, pp. 140–149.

Göessel, M., Ocheretny, V., Sogomonyan, E., and Marienfeld, D., New Methods of Concurrent Checking, Dordrecht: Springer Science+Business Media B.V., 2008.

Goessel, M., Saposhnikov, Vl., Saposhnikov, V., and Dmitriev, A., A new method for concurrent checking by use of a 1-out-of-4 code, Proceedings of the 6th IEEE International On-line Testing Workshop, Palma de Mallorca, 2000, pp. 147–152. https://doi.org/10.1109/OLT.2000.856627

Saposhnikov, V.V., Morozov, A., Saposhnikov, Vl.V., and Goessel, M., Concurrent checking by use of complementary circuits for 1-out-of-3 codes, 5th International Workshop IEEE DDECS 2002, Brno, 2002.

Sapozhnikov, V.V., Sapozhnikov, Vl.V., Dmitriev, A.V., Morozov, A.V., and Gessel’, M., Organization of the functional control of combinational circuits by the method of logical complement, Elektron. Model., 2002, vol. 24, no. 6, pp. 52–66.

Gessel, M., Morozov, A.V., Sapozhnikov, V.V., and Sapozhnikov, Vl.V., Logic complement, a new method of checking the combinational circuits, Autom. Remote Control, 2003, vol. 64, no. 1, pp. 153–161.

Goessel, M., Morozov, A.V., Sapozhnikov, V.V., and Sapozhnikov, Vl.V., Checking combinational circuits by the method of logic complement, Autom. Remote Control, 2005, vol. 66, no. 8, pp. 1336–1346.

Sen, S.K. and Roy, S.S., An optimized concurrent self-checker using constraint-don’t cares and 1-out-of-4 code, National Conference (AECDISC-2008) in Asansol Engineering College, 2008.

Sen, S.K., A self-checking circuit for concurrent checking by 1-out-of-4 code with design optimization using constraint don’t cares, National Conference on Emerging Trends and Advances in Electrical Engineering and Renewable Energy (NCEEERE 2010), 2010.

Das, D.K., Roy, S.S., Dmitiriev, A., Morozov, A., and Gössel, M., Constraint don’t cares for optimizing designs for concurrent checking by 1-out-of-3 codes, Proceedings of the 10th International Workshops on Boolean Problems, Freiberg, September, 2012, pp. 33–40.

Efanov, D., Sapozhnikov, V., and Sapozhnikov, Vl., Methods of organization of totally self-checking concurrent error detection system on the basis of constant-weight “1-out-of-3” code, Proceedings of 14th IEEE East-West Design & Test Symposium (EWDTS`2016), Yerevan, 2016, pp. 117–125. https://doi.org/10.1109/EWDTS.2016.7807622

Sapozhnikov, V.V., Sapozhnikov, Vl.V., and Efanov, D.V., The construction of fully self-checking structures of functional control systems using the constant-weight “1-out-of-3”-code, Elektron. Model., 2016, vol. 38, no. 6, pp. 25–43.

Sapozhnikov, V.V., Sapozhnikov, Vl.V., Efanov, D.V., and Pivovarov, D.V., The logical complement method based on the constant-weight “1-out-of-3”-code for constructing fully self-checking structures of functional control systems, Elektron. Model., 2017, vol. 39, no. 2, pp. 15–34.

Sapozhnikov, V.V., Sapozhnikov, Vl.V., and Efanov, D.V., The method of functional control of combinational logic devices based on code “2-out-of-4” code, Izv. Vyssh. Uchebn. Zaved.,Priborostr., 2016, vol. 59, no. 7, pp. 524–533. https://doi.org/10.17586/0021-3454-2016-59-7-524-533

Sapozhnikov, V.V., Sapozhnikov, Vl.V., and Efanov, D.V., The construction of self-checking structures of functional control systems based on the constant-weight “1-out-of-3”-code, Probl. Upr., 2017, no. 1, pp. 57–64.

Morozov, A., Saposhnikov, V.V., Saposhnikov, Vl.V., and Goessel, M., New self-checking circuits by use of Berger-codes, Proceedings of 6th IEEE International On-Line Testing Workshop, Palma De Mallorca, 2000, pp. 171–176. https://doi.org/10.1109/OLT.2000.856626

Berger, J.M., A note on error detection codes for asymmetric channels, Inf. Control, 1961, vol. 4, no. 1, pp. 68–73. https://doi.org/10.1016/S0019-9958(61)80037-5

Sapozhnikov, V.V., Sapozhnikov, Vl.V., Efanov, D.V., and Pivovarov, D.V., A method of constructing a functional control system based on logical complement using the constant-weight “1-out-of-5”-code, Radioelektron. Inf., 2017, no. 3, pp. 15–22.

Pivovarov, D.V., Construction of functional control systems for multi-output combinational circuits by the method of logical complement using constant-weight codes, Avtom. Transp., 2018, vol. 4, no. 1, pp. 130–148.

Carter, W.C., Duke, K.A., and Schneider, P.R., US Patent 747533, 1968.

Sapozhnikov, V.V. and Sapozhnikov, Vl.V., Samoproveryaemye diskretnye ustroistva (Self-Checking Discrete Devices), St. Petersburg: Energoatomizdat, 1992.

Aksenova, G.P., Necessary and sufficient conditions for constructing fully verifiable convolution schemes modulo 2, Avtom. Telemekh., 1979, no. 9, pp. 126–135.

Author information

Authors and Affiliations

Corresponding authors

Ethics declarations

The authors declare that they do not have any conflicts of interest.

Additional information

Translated by K. Lazarev

About this article

Cite this article

Efanov, D.V., Sapozhnikov, V.V., Sapozhnikov, V.V. et al. Synthesis of Built-in Self-Test Control Circuits Based on the Method of Boolean Complement to Constant-Weight 1-out-of-n Codes. Aut. Control Comp. Sci. 53, 481–491 (2019). https://doi.org/10.3103/S014641161906004X

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.3103/S014641161906004X